## Transistors and Logic Circuits

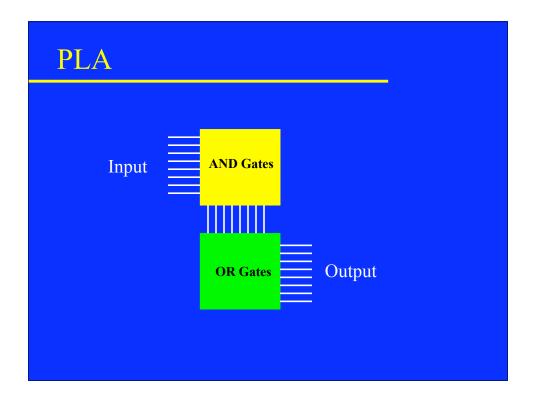

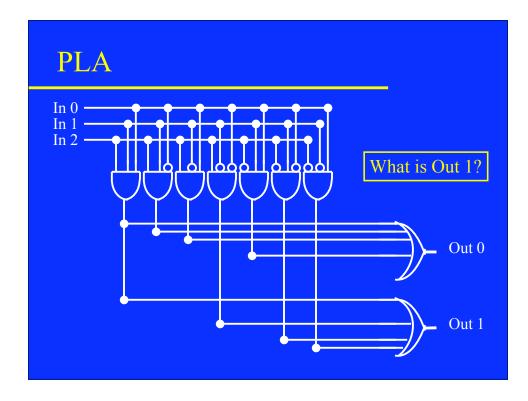

## Programmable Logic Array

- Any Logic Truth Table can be implemented

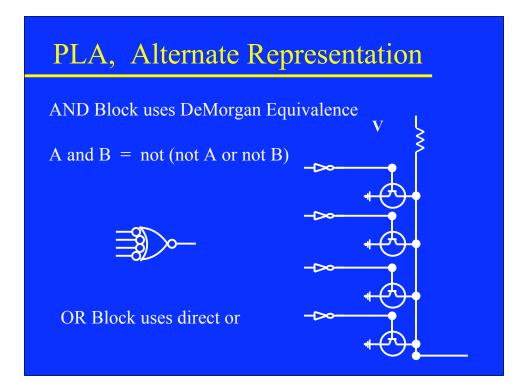

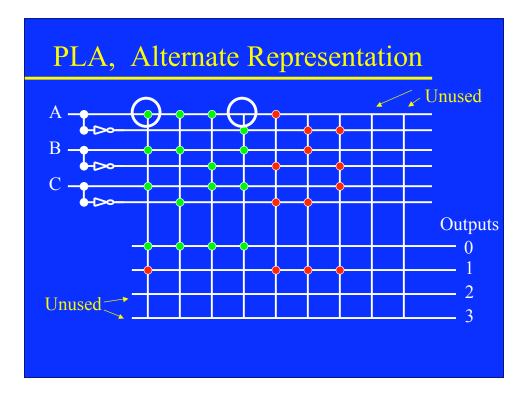

- Uses block of AND gates followed by block of OR gates

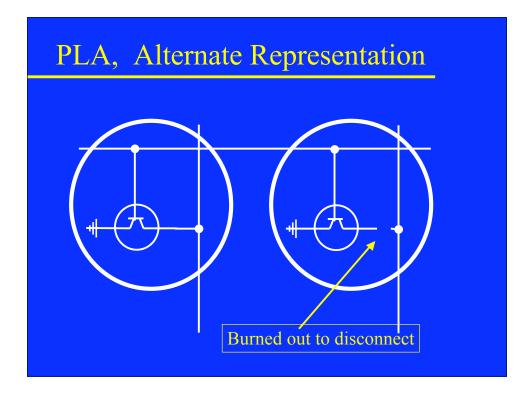

- Programmable

- once

- many times

- Used for implementing different circuits

| A | В    | С     |   |    |     |    |     |    |

|---|------|-------|---|----|-----|----|-----|----|

| e | xpre | ssion |   | Α  | and | В  | and | С  |

| 1 | 1    | 1     | 1 | А  | and | в  | and | ~C |

| 1 | 1    | 0     | 1 | А  | and | ~B | and | С  |

| 1 | 0    | 1     | 1 |    |     |    |     |    |

| 1 | 0    | 0     | 0 | ~A | and | в  | and | С  |

| 0 | 1    | 1     | 1 |    |     |    |     |    |

| 0 | 1    | 0     | 0 |    |     |    |     |    |

| 0 | 0    | 1     | 0 |    |     |    |     |    |

| A | В | С | expression | n               |

|---|---|---|------------|-----------------|

| 1 | 1 | 1 | 1          | A and B and C   |

| 1 | 1 | 0 | 0          | Odd Parity      |

| 1 | 0 | 1 | 0          | Ouurany         |

| 1 | 0 | 0 | 1          | A and ~B and ~C |

| 0 | 1 | 1 | 0          |                 |

| 0 | 1 | 0 | 1          | ~A and B and ~C |

| 0 | 0 | 1 | 1          | ~A and ~B and C |

| 0 | 0 | 0 | 0          |                 |

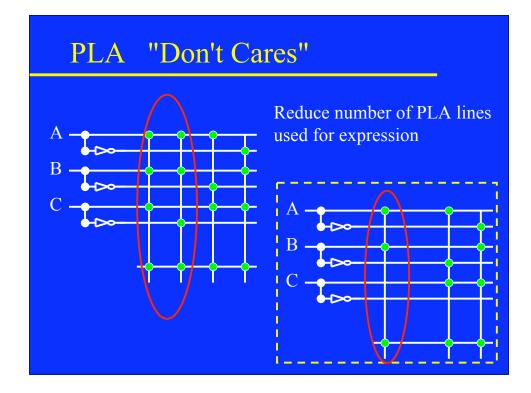

| P | PLA | "] | Don't                               | Cares     | 11 |   |     |

|---|-----|----|-------------------------------------|-----------|----|---|-----|

| A | в   | С  | exp                                 | А         | в  | С | exp |

| 1 | 1   | 1  | 1 —                                 | 1         | 1  | x | 1   |

| 1 | 1   | 0  | 1 🦯                                 |           |    |   |     |

| 1 | 0   | 1  | 1                                   | 1         | 0  | 1 | 1   |

| 1 | 0   | 0  | 0                                   | 1         | 0  | 0 | 0   |

| 0 | 1   | 1  | 1                                   | 0         | 1  | 1 | 1   |

| 0 | 1   | 0  | 0                                   | 0         | 1  | 0 | 0   |

| 0 | 0   | 1  | 0                                   | 0         | 0  | 1 | 0   |

| 0 | 0   | 0  | 0                                   | 0         | 0  | 0 | 0   |

|   |     |    | $\mathbf{x} = \mathbf{D}\mathbf{c}$ | on't Care |    |   |     |