| C<br>Muxe  | <ul> <li>Instruction Critical Paths</li> <li>Calculate cycle time assuming negligible delays (for muxes, control unit, sign extend, PC access, shift left 2, wires, setup and hold times) except:</li> </ul> |        |        |       |              |       |       |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------|--------------|-------|-------|--|

| •          | <ul> <li>Instruction and Data Memory (200 ps)</li> </ul>                                                                                                                                                     |        |        |       |              |       |       |  |

| •          | <ul> <li>ALU and adders (100 ps)</li> </ul>                                                                                                                                                                  |        |        |       |              |       |       |  |

| •          | <ul> <li>Register File access (reads or writes) (100 ps)</li> </ul>                                                                                                                                          |        |        |       |              |       |       |  |

|            |                                                                                                                                                                                                              |        |        | DM    | <b>D</b> 14/ | ]     |       |  |

| Instr.     | I Mem                                                                                                                                                                                                        | Reg Rd | ALU Op | D Mem | Reg Wr       | Total |       |  |

| R-<br>type | 200                                                                                                                                                                                                          | 100    | 100    |       | 100          | 500   |       |  |

| load       | 200                                                                                                                                                                                                          | 100    | 100    | 200   | 100          | 700   |       |  |

| store      | 200                                                                                                                                                                                                          | 100    | 100    | 200   |              | 600   |       |  |

| beq        | 200                                                                                                                                                                                                          | 100    | 100    |       |              | 400   |       |  |

| jump       | 200                                                                                                                                                                                                          |        |        |       |              | 200   |       |  |

| Page 3     |                                                                                                                                                                                                              |        |        |       |              |       | g 201 |  |

|                                                                                                                             |        | J Contr |           | e decodina la | عرواه |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------|---------|-----------|---------------|-------|--|

| <ul> <li>ontrolling the ALU uses of multiple decoding levels</li> <li>main control unit generates the ALUOp bits</li> </ul> |        |         |           |               |       |  |

|                                                                                                                             | •      |         | ALUcontro | •             |       |  |

| Instrop funct ALUOp action ALUcontrol                                                                                       |        |         |           |               |       |  |

| lw                                                                                                                          | XXXXXX | 00      | add       | 0110          |       |  |

| sw                                                                                                                          | XXXXXX | 00      | add       | 0110          |       |  |

| beq                                                                                                                         | XXXXXX | 01      | subtract  | 1110          |       |  |

| add                                                                                                                         | 100000 | 10      | add       | 0110          |       |  |

| subt                                                                                                                        | 100010 | 10      | subtract  | 1110          |       |  |

| and                                                                                                                         | 100100 | 10      | and       | 0000          |       |  |

| or                                                                                                                          | 100101 | 10      | or        | 0001          |       |  |

| xor                                                                                                                         | 100110 | 10      | xor       | 0010          |       |  |

| nor                                                                                                                         | 100111 | 10      | nor       | 0011          |       |  |

| slt                                                                                                                         | 101010 | 10      | slt       | 1111          |       |  |

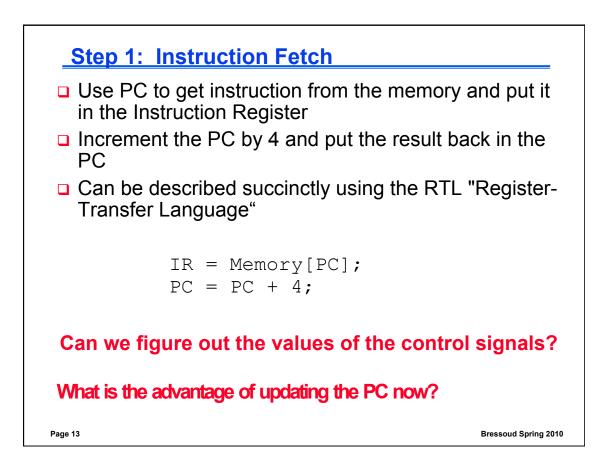

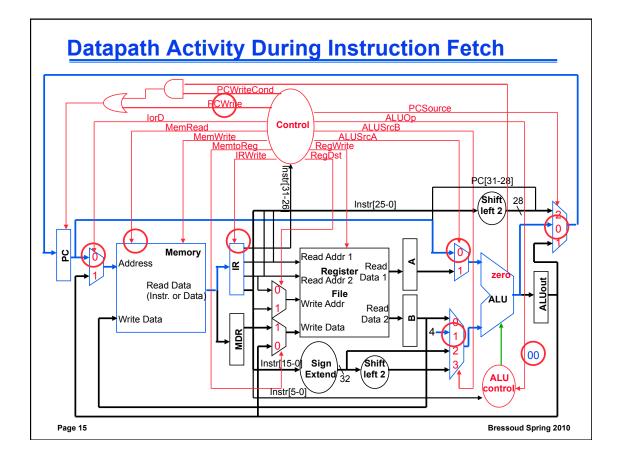

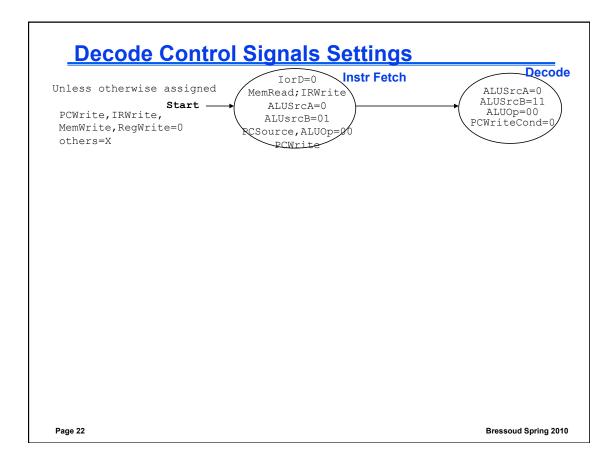

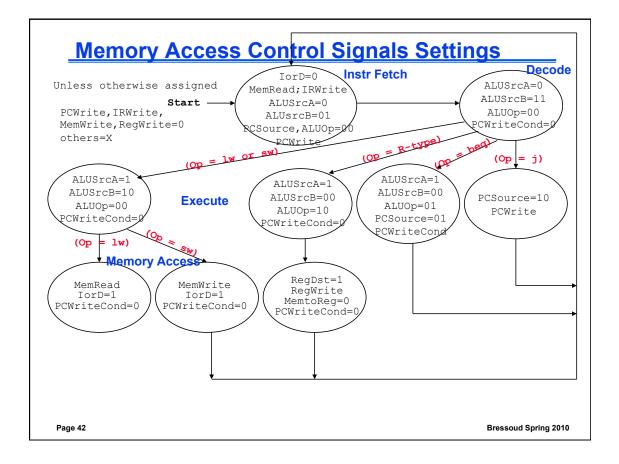

| Fetch Control S | Signals Settings |                      |

|-----------------|------------------|----------------------|

| Page 17         |                  | Bressoud Spring 2010 |

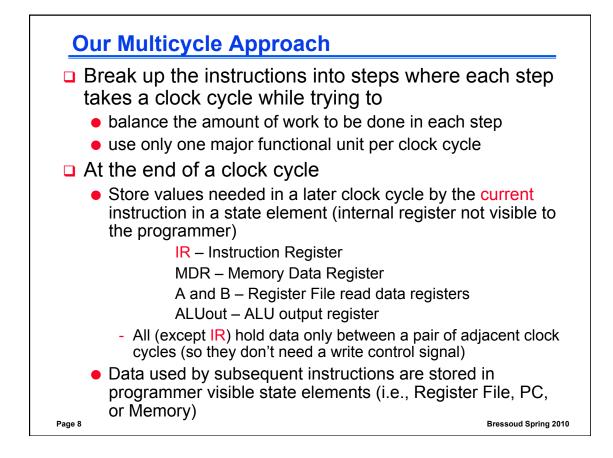

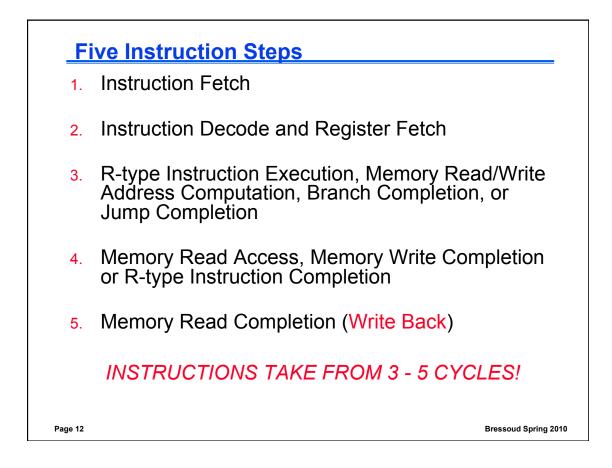

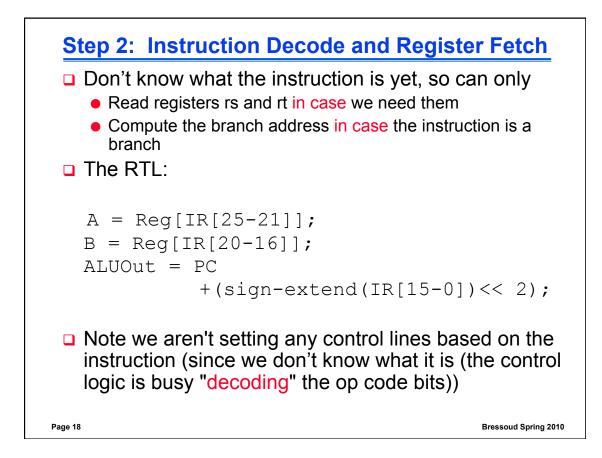

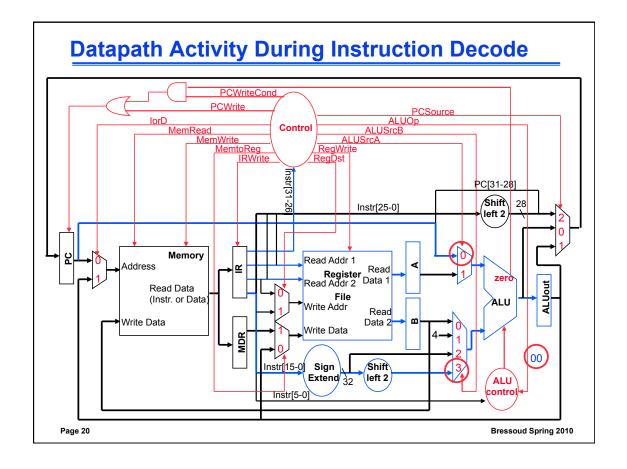

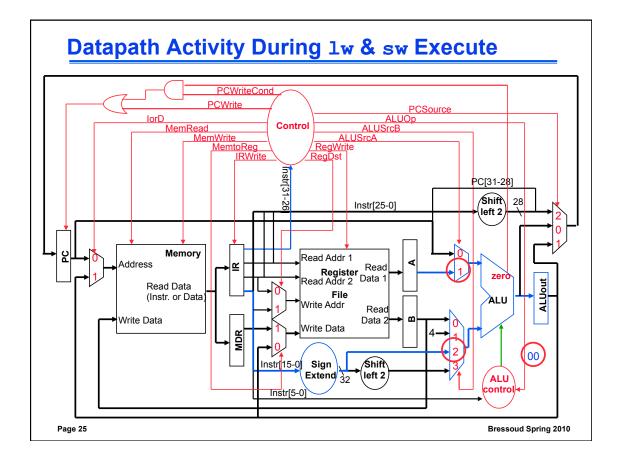

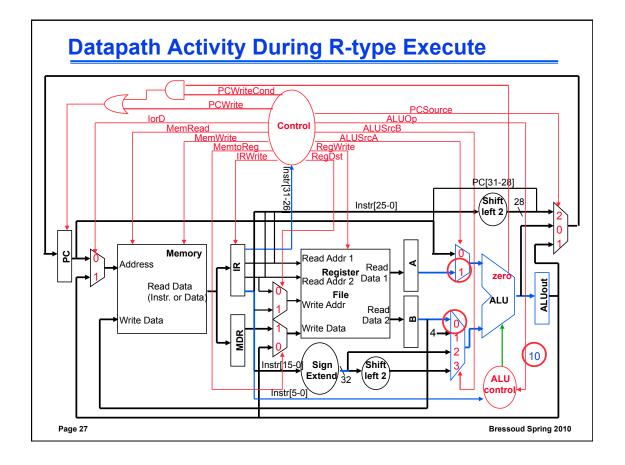

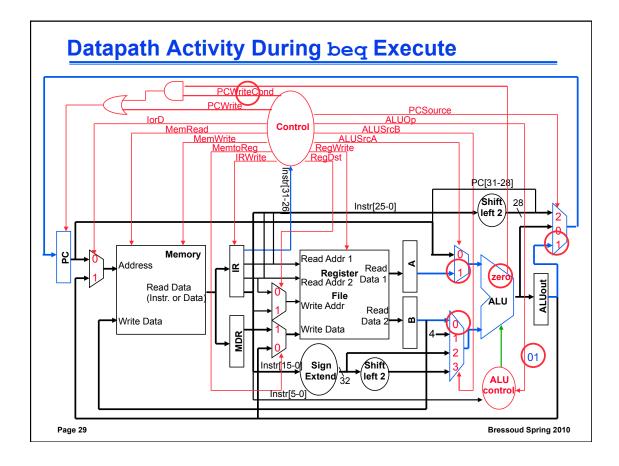

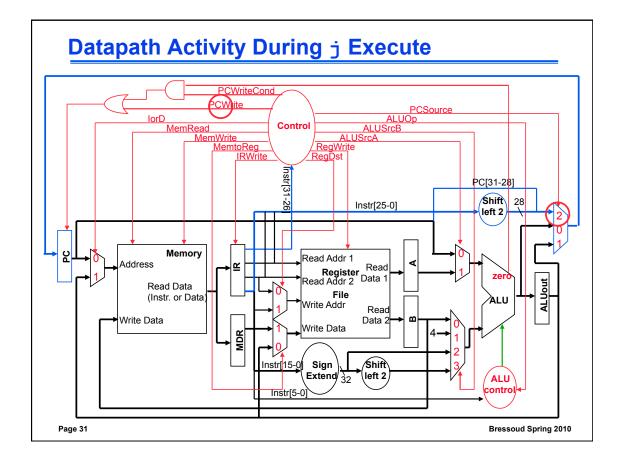

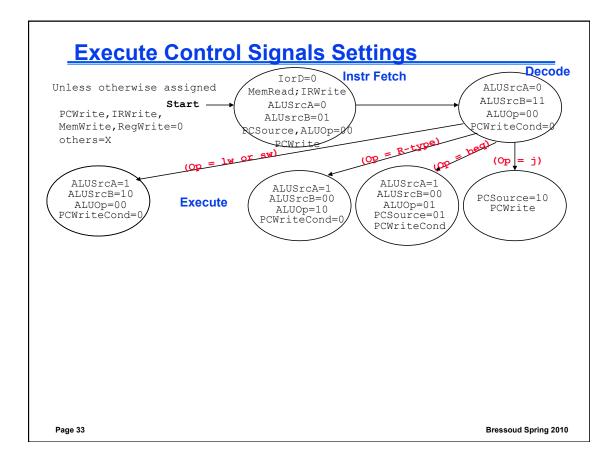

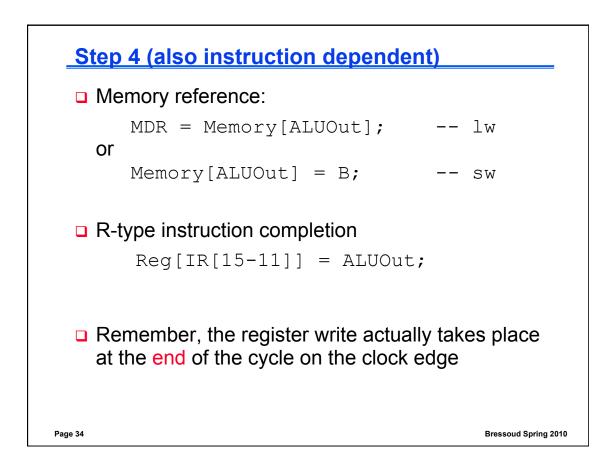

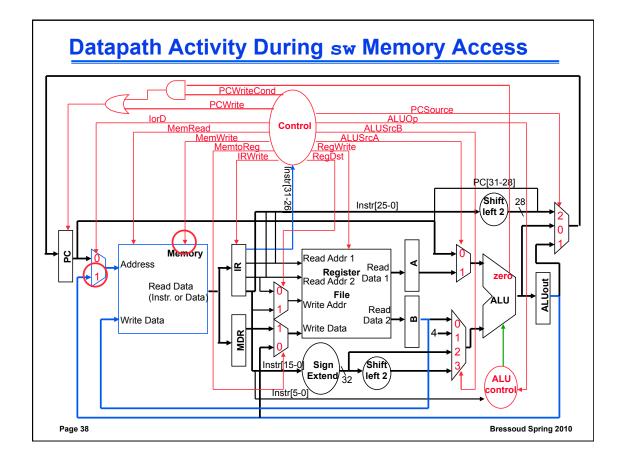

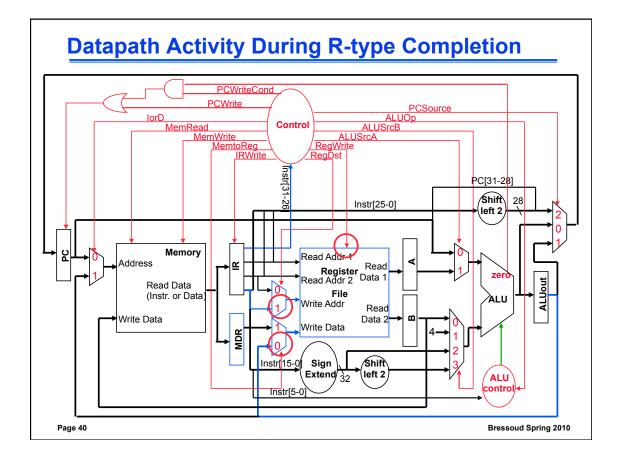

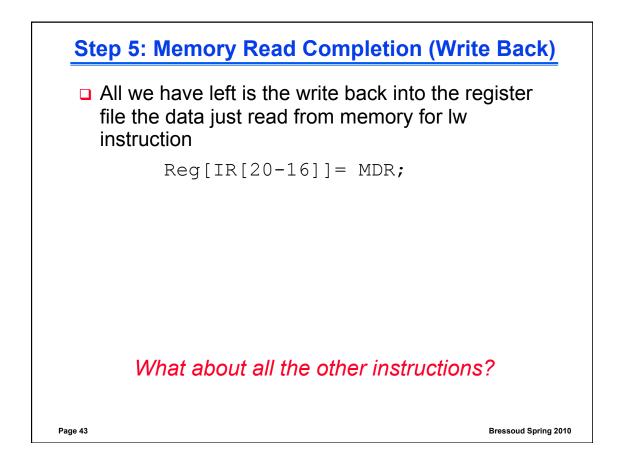

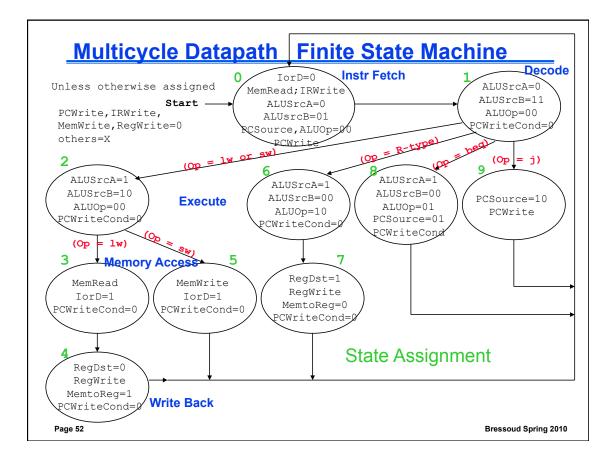

## Step 3 (instruction dependent) ALU is performing one of four functions, based on instruction type Memory reference (lw and sw): ALUOut = A + sign-extend(IR[15-0]); R-type: ALUOut = A op B; Branch: if (A==B) PC = ALUOut; Jump: PC = PC[31-28] || (IR[25-0] << 2);</pre>

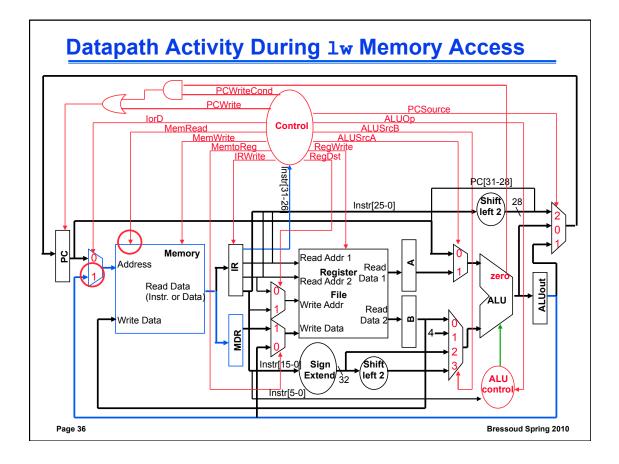

| Instr<br>fetch       IR = Memory[PC];<br>PC = PC + 4;         Decode       A = Reg[IR[25-21]];<br>B = Reg[IR[20-16]];<br>ALUOUt = PC + (sign-extend(IR[15-0]) << 2         Execute       ALUOUt =<br>A op B;       ALUOUt =<br>A + sign-extend<br>(IR[15-0]);       if<br>PC =<br>(A==B)<br>PC =<br>III(<br>ALUOUt;       PC =<br>[31-28]<br>PC =<br>III(<br>ALUOUt;         Memory       Deg[IR       MDD = Memory       Image: NDD = Memory | PC         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| B = Reg[IR[20-16]];         ALUOut = PC + (sign-extend (IR[15-0]) << 2                                                                                                                                                                                                                                                                                                                                                                        | PC         |

| A op B; A + sign-extend (A==B) [31-28<br>(IR[15-0]); PC =   (<br>ALUOUt; [25-0]<br>2)                                                                                                                                                                                                                                                                                                                                                         |            |

| Momony Dog [ID MDD - Momony                                                                                                                                                                                                                                                                                                                                                                                                                   | IR<br>] << |

| Memory<br>access<br>[15-11]] = ALUOut;<br>ALUOut;<br>Memory[ALUOut]<br>= B;                                                                                                                                                                                                                                                                                                                                                                   |            |

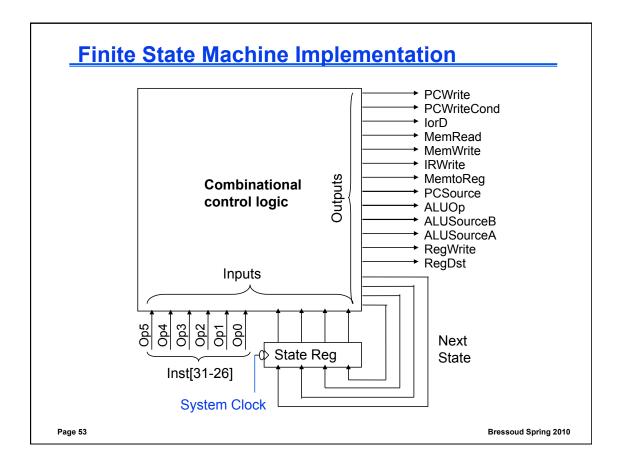

| Outputs     | Input Values (Current State[3-0]) |      |      |      |      |      |      |      |      |      |

|-------------|-----------------------------------|------|------|------|------|------|------|------|------|------|

|             | 0000                              | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

| PCWrite     | 1                                 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| PCWriteCond | Х                                 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | Х    |

| lorD        | 0                                 | Х    | Х    | 1    | Х    | 1    | Х    | Х    | Х    | Х    |

| MemRead     | 1                                 | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    |

| MemWrite    | 0                                 | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    |

| IRWrite     | 1                                 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| MemtoReg    | Х                                 | Х    | Х    | Х    | 1    | Х    | Х    | 0    | Х    | Х    |

| PCSource    | 00                                | XX   | 01   | 10   |

| ALUOp       | 00                                | 00   | 00   | XX   | XX   | XX   | 10   | XX   | 01   | XX   |

| ALUSrcB     | 01                                | 11   | 10   | XX   | XX   | XX   | 00   | XX   | 00   | XX   |

| ALUSrcA     | 0                                 | 0    | 1    | Х    | Х    | Х    | 1    | Х    | 1    | Х    |

| RegWrite    | 0                                 | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    |

| RegDst      | Х                                 | Х    | Х    | Х    | 0    | Х    | Х    | 1    | Х    | Х    |

## Datapath Control Outputs Truth Table

| Current |        | Ins    | st[31-26] | (Op[5- | ·0])   |         |

|---------|--------|--------|-----------|--------|--------|---------|

| State   | 000000 | 000010 | 000100    | 100011 | 101011 | Any     |

| [3-0]   | (R-    | (jmp)  | (beq)     | (lw)   | (sw)   | other   |

|         | type)  |        |           |        |        |         |

| 0000    | 0001   | 0001   | 0001      | 0001   | 0001   | 0001    |

| 0001    | 0110   | 1001   | 1000      | 0010   | 0010   | illegal |

| 0010    | XXXX   | XXXX   | XXXX      | 0011   | 0101   | illegal |

| 0011    | XXXX   | XXXX   | XXXX      | 0100   | XXXX   | illegal |

| 0100    | XXXX   | XXXX   | XXXX      | 0000   | XXXX   | illegal |

| 0101    | XXXX   | XXXX   | XXXX      | XXXX   | 0000   | illegal |

| 0110    | 0111   | XXXX   | XXXX      | XXXX   | XXXX   | illegal |

| 0111    | 0000   | XXXX   | XXXX      | XXXX   | XXXX   | illegal |

| 1000    | XXXX   | XXXX   | 0000      | XXXX   | XXXX   | illegal |

| 1001    | XXXX   | 0000   | XXXX      | XXXX   | XXXX   | illegal |

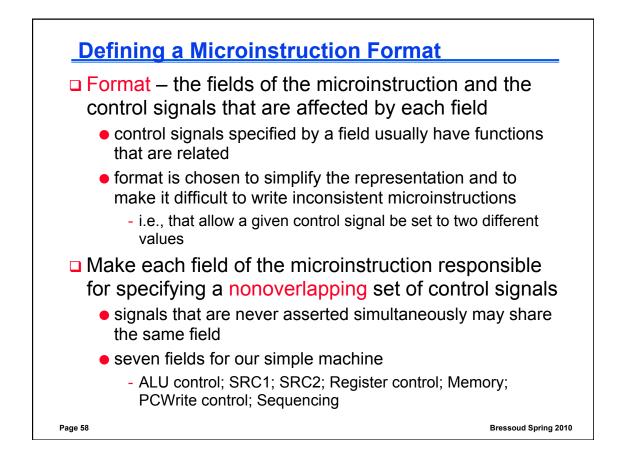

| Field            | Value        | Signal setting                           | Comments                                                                        |

|------------------|--------------|------------------------------------------|---------------------------------------------------------------------------------|

| ALU              | Add          | ALUOp = 00                               | Cause ALU to add                                                                |

| control          | Subt         | ALUOp = 01                               | Cause ALU to subtract (compare op for beq)                                      |

|                  | Func code    | ALUOp = 10                               | Use IR function code to determine ALU contro                                    |

| SRC1             | PC           | ALUSrcA = 0                              | Use PC as top ALU input                                                         |

|                  | А            | ALUSrcA = 1                              | Use reg A as top ALU input                                                      |

| SRC2             | В            | ALUSrcB = 00                             | Use reg B as bottom ALU input                                                   |

|                  | 4            | ALUSrcB = 01                             | Use 4 as bottom ALU input                                                       |

|                  | Extend       | ALUSrcB = 10                             | Use sign ext output as bottom ALU input                                         |

|                  | Extshft      | ALUSrcB = 11                             | Use shift-by-two output as bottom ALU input                                     |

| Register control | Read         |                                          | Read RegFile using rs and rt fields of IR as read addr's; put data into A and B |

|                  | Write ALU    | RegWrite,<br>RegDst = 1,<br>MemtoReg = 0 | Write RegFile using rd field of IR as write addr<br>and ALUOut as write data    |

|                  | Write<br>MDR | RegWrite,<br>RegDst = 0,<br>MemtoReg = 1 | Write RegFile using rt field of IR as write addr<br>and MDR as write data       |

| Field               | Value           | Signal setting                | Comments                                                                    |

|---------------------|-----------------|-------------------------------|-----------------------------------------------------------------------------|

| Memory              | Read PC         | MemRead,<br>lorD = 0,IRWrite  | Read memory using PC as addr; write result into IR (and MDR)                |

|                     | Read ALU        | MemRead,<br>lorD = 1          | Read memory using ALUOut as addr; write results into MDR                    |

|                     | Write ALU       | MemWrite,<br>IorD = 1         | Write memory using ALUOut as addr and B as write data                       |

| PC write<br>control | ALU             | PCSource = 00<br>PCWrite      | Write PC with output of ALU                                                 |

|                     | ALUOut-<br>cond | PCSource = 01,<br>PCWriteCond | If Zero output of ALU is true, write PC with the contents of ALUOut         |

|                     | Jump<br>address | PCSource = 10,<br>PCWrite     | Write PC with IR jump address after shift-by-two                            |

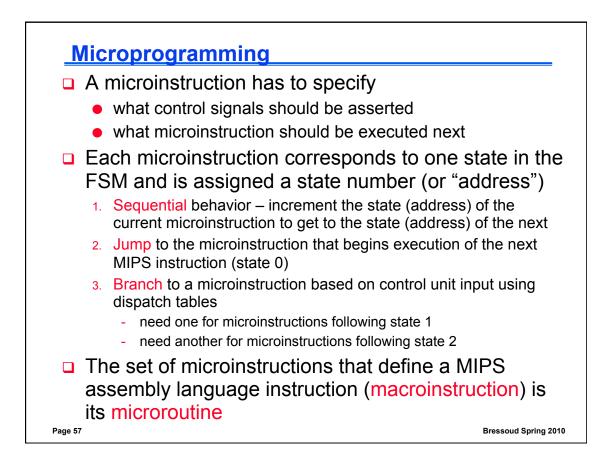

| Sequen-<br>cing     | Seq             | AddrCtl = 11                  | Choose next microinstruction sequentially                                   |

|                     | Fetch           | AddrCtl = 00                  | Jump to the first microinstruction (i.e., Fetch) to begin a new instruction |

|                     | Dispatch 1      | AddrCtl = 01                  | Branch using PLA_1                                                          |

|                     | Dispatch 2      | AddrCtl = 10                  | Branch using PLA_2                                                          |

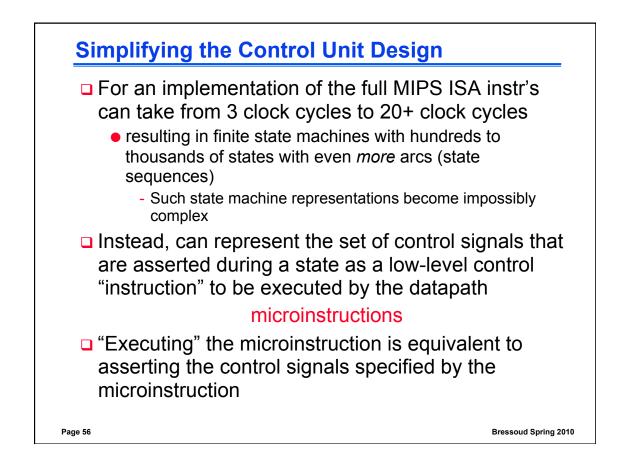

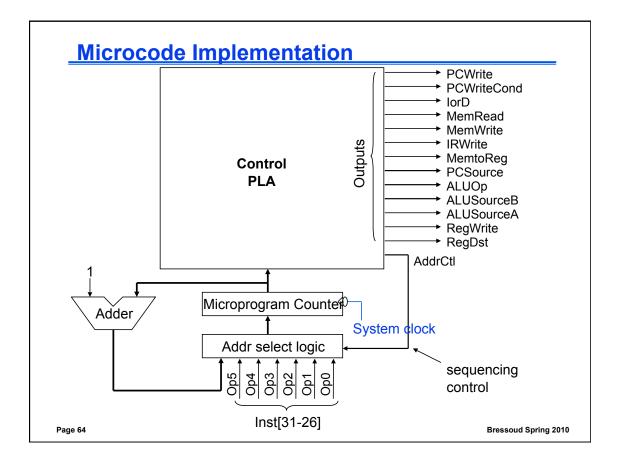

## Creating the Microprogram

## Fetch microinstruction

| Label<br>(Addr)     | ALU<br>control | SRC1 | SRC2 | Reg<br>control | Memory  | PCWrite control | Seq'ing |

|---------------------|----------------|------|------|----------------|---------|-----------------|---------|

| Fetch<br><b>(0)</b> | Add            | PC   | 4    |                | Read PC | ALU             | Seq     |

| compute PC + 4                                   | fetch instr write ALU go to μinstr<br>into IR output into 1<br>PC |

|--------------------------------------------------|-------------------------------------------------------------------|

| Label field represents the s<br>microinstruction | state (address) of the                                            |

| Fetch microinstruction assi                      | gned state (address) 0                                            |

| Page 62                                          | Bressoud Spring 2010                                              |

| Addr         | ALU<br>control | SRC1 | SRC2        | Reg<br>control | Memory       | PCWrite control | Seq'ing |

|--------------|----------------|------|-------------|----------------|--------------|-----------------|---------|

| 0            | Add            | PC   | 4           |                | Read PC      | ALU             | Seq     |

| 1            | Add            | PC   | Ext<br>shft | Read           |              |                 | Disp 1  |

| 2            | Add            | А    | Extend      |                |              |                 | Disp 2  |

| 3            |                |      |             |                | Read ALU     |                 | Seq     |

| 4            |                |      |             | Write<br>MDR   |              |                 | Fetch   |

| 5            |                |      |             |                | Write<br>ALU |                 | Fetch   |

| 6            | Func<br>code   | A    | В           |                |              |                 | Seq     |

| 7            |                |      |             | Write<br>ALU   |              |                 | Fetch   |

| 8            | Subt           | A    | В           |                |              | ALUOut-<br>cond | Fetch   |

| 9<br>Page 63 |                |      |             |                |              | Jump<br>address | Fetch   |

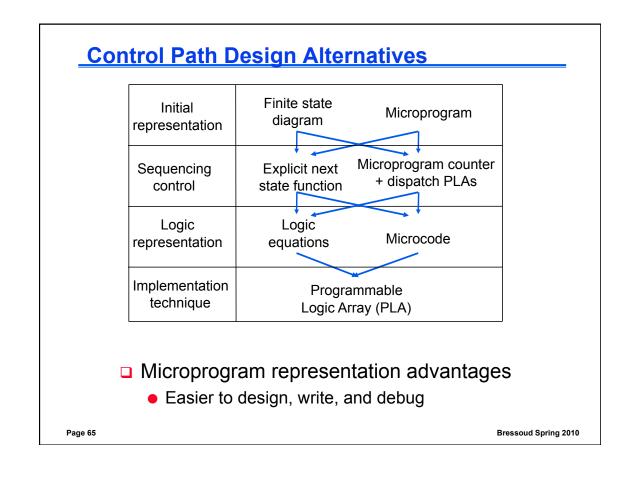

| Single Cycle vs. Multi<br>Single Cycle Implementation:                                              | ple Cycle Timing                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cik                                                                                                 | Cycle 2                                                                                                                                                                                                |

| lw                                                                                                  | sw Waste                                                                                                                                                                                               |

| Multiple Cycle Implementation:<br>Clk Cycle ‡ Cycle ‡ Cycle ¥ Cycle<br>Lw<br>IFetch Dec Exec Mem WB | multicycle clock<br>slower than 1/5 <sup>th</sup> of<br>single cycle clock<br>due to state register<br>overhead<br>Cycle 6 Cycle 7 Cycle 8 Cycle 9 Cycle 10<br>Sw R-type<br>IFetch Dec Exec Mem IFetch |

| Page 67                                                                                             | Bressoud Spring 2010                                                                                                                                                                                   |