### addx

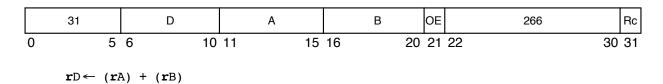

Add (x'7C00 0214')

| rD,rA,rB | (OE = 0 Rc = 0)      |

|----------|----------------------|

| rD,rA,rB | (OE = 0 Rc = 1)      |

| rD,rA,rB | (OE = 1 Rc = 0)      |

| rD,rA,rB | (OE = 1 Rc = 1)      |

|          | rD,rA,rB<br>rD,rA,rB |

The sum  $(\mathbf{r}A) + (\mathbf{r}B)$  is placed into  $\mathbf{r}D$ .

The **add** instruction is preferred for addition because it sets few status bits.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (If Rc = 1)

**NOTE:** CR0 field may not reflect the infinitely precise result if overflow occurs (see next bullet item.

• XER:

Affected: SO, OV

(If OE = 1)

**NOTE:** For more information on condition codes see Section 2.1.3, "Condition Register," and Section 2.1.5, "XER Register."

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | ХО   |

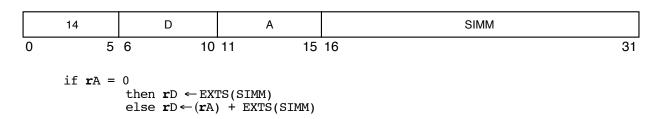

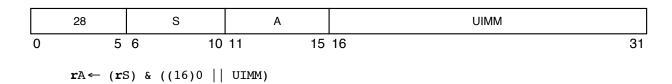

addi

Add Immediate (x'3800 0000')

addi rD,rA,SIMM

The sum  $(\mathbf{r}A|\mathbf{0})$  + sign extended SIMM is placed into  $\mathbf{r}D$ .

The addi instruction is preferred for addition because it sets few status bits.

**NOTE:** addi uses the value 0, not the contents of GPR0, if  $\mathbf{r}A = 0$ .

Other registers altered:

• None

Simplified mnemonics:

| li   | rD,value    | equivalent to | addi | <b>r</b> D <b>,0</b> ,value |

|------|-------------|---------------|------|-----------------------------|

| la   | rD,disp(rA) | equivalent to | addi | rD,rA,disp                  |

| subi | rD,rA,value | equivalent to | addi | rD,rA,-value                |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

8

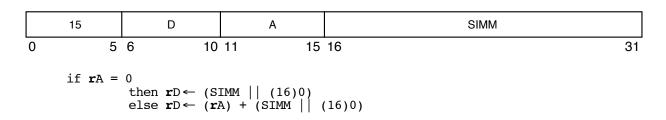

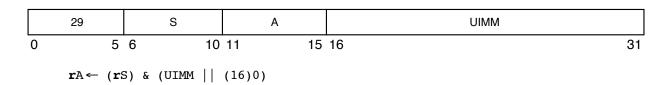

addis

addis

Add Immediate Shifted (x'3C00 0000')

rD,rA,SIMM addis

The sum  $(\mathbf{r}A|0) + (SIMM \parallel 0x0000)$  is placed into  $\mathbf{r}D$ .

The addis instruction is preferred for addition because it sets few status bits.

**NOTE:** addis uses the value 0, not the contents of GPR0, if  $\mathbf{r}A = 0$ .

Other registers altered:

• None

| lis   | <b>r</b> D,value | equivalent to | addis rD,0,value   |

|-------|------------------|---------------|--------------------|

| subis | rD,rA,value      | equivalent to | addis rD,rA,-value |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

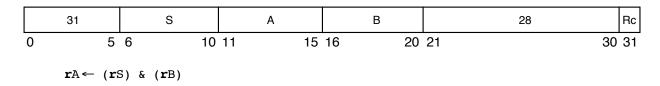

AND (x'7C00 0038')

andx

| and  | rA,rS,rB | (Rc = 0) |

|------|----------|----------|

| and. | rA,rS,rB | (Rc = 1) |

The contents of **r**S are ANDed with the contents of **r**B and the result is placed into **r**A. Other registers altered:

- Condition Register (CR0 field):

- Affected: LT, GT, EQ, SO (If Rc = 1)

| PowerPC Architecture Level |      | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------|------------------|------------------|------|

|                            | UISA |                  |                  | Х    |

andi.

# andi.

AND Immediate (x'7000 0000')

andi. rA,rS,UIMM

The contents of  $\mathbf{r}S$  are ANDed with  $0x000 \parallel \text{UIMM}$  and the result is placed into  $\mathbf{r}A$ .

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO

8

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

andis.

andis.

AND Immediate Shifted (x'7400 0000')

andis. rA,rS,UIMM

The contents of **rS** are ANDed with UIMM  $\parallel 0x0000$  and the result is placed into **r**A.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

## **b**x

Branch (x'4800 0000')

| b   | target_addr | (AA = 0 LK = 0) |

|-----|-------------|-----------------|

| ba  | target_addr | (AA = 1 LK = 0) |

| bl  | target_addr | (AA = 0 LK = 1) |

| bla | target_addr | (AA = 1 LK = 1) |

|   | 18                 | LI                                                                                             | AA LK    |

|---|--------------------|------------------------------------------------------------------------------------------------|----------|

| 0 | 5                  | 6                                                                                              | 29 30 31 |

|   | if AA =<br>if LK = | then NIA $\leftarrow$ iea EXTS(LI    0b00)<br>else NIA $\leftarrow$ iea CIA + EXTS(LI    0b00) |          |

target\_addr specifies the branch target address.

If AA = 1, then the branch target address is the value LI || 0b00 sign-extended.

If AA = 0, then the branch target address is the sum of LI  $\parallel 0b00$  sign-extended plus the address of this instruction.

If LK = 1, then the effective address of the instruction following the branch instruction is placed into the link register.

Other registers altered:

Affected: Link Register (LR) (If LK = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | I    |

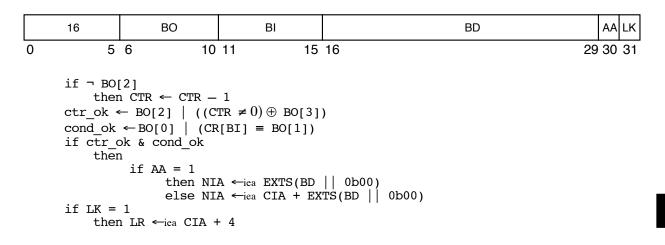

## **bc***x*

Branch Conditional (x'4000 0000')

| bc   | BO,BI,target_addr | (AA = 0 LK = 0) |

|------|-------------------|-----------------|

| bca  | BO,BI,target_addr | (AA = 1 LK = 0) |

| bcl  | BO,BI,target_addr | (AA = 0 LK = 1) |

| bcla | BO,BI,target_addr | (AA = 1 LK = 1) |

The BI field specifies the bit in the condition register (CR) to be used as the condition of the branch. The BO field is encoded as described in Table 8-6. Additional information about BO field encoding is provided in Section 4.2.4.2, "Conditional Branch Control".

| Table 8-6. | BO Operand | Encodings |

|------------|------------|-----------|

|------------|------------|-----------|

| во                                                                                                                                                                                                                                                                                                                                                                              | Description                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

| 0000 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR 0 and the condition is FALSE.   |  |

| 0001 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR = 0 and the condition is FALSE. |  |

| 001 <i>zy</i>                                                                                                                                                                                                                                                                                                                                                                   | Branch if the condition is FALSE.                                                     |  |

| 0100 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR 0 and the condition is TRJE.    |  |

| 0101 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR = 0 and the condition is TRUE.  |  |

| 011 <i>zy</i>                                                                                                                                                                                                                                                                                                                                                                   | Branch if the condition is TRUE.                                                      |  |

| 1 <i>z</i> 00 <i>y</i>                                                                                                                                                                                                                                                                                                                                                          | Decrement the CTR, then branch if the decremented CTR 0.                              |  |

| 1 <i>z</i> 01 <i>y</i>                                                                                                                                                                                                                                                                                                                                                          | Decrement the CTR, then branch if the decremented CTR = 0.                            |  |

| 1 <i>z</i> 1 <i>zz</i>                                                                                                                                                                                                                                                                                                                                                          | Branch always.                                                                        |  |

| In this table, <i>z</i> indicates a bit that is ignored.<br><b>Note:</b> The <i>z</i> bits should be cleared, as they may be assigned a meaning in some future version of the<br>PowerPC architecture.<br>The <i>y</i> bit provides a hint about whether a conditional branch is likely to be taken, and may be used by some<br>PowerPC implementations to improve performance. |                                                                                       |  |

target\_addr specifies the branch target address.

If AA = 0, the branch target address is the sum of BD || 0b00 sign-extended and the address of this instruction.

If AA = 1, the branch target address is the value BD || 0b00 sign-extended.

If LK = 1, the effective address of the instruction following the branch instruction is placed into the link register.

Other registers altered:

|                    | Affected: Count Register (CTR)         |                                                 | (If BO[2] = 0) |                                           |

|--------------------|----------------------------------------|-------------------------------------------------|----------------|-------------------------------------------|

|                    | Affected: Link Register (LR)           |                                                 | (If LK = 1)    |                                           |

| Simpl              | ified mnemonics:                       |                                                 |                |                                           |

| blt<br>bne<br>bdnz | target<br><b>cr2</b> ,target<br>target | equivalent to<br>equivalent to<br>equivalent to | bc<br>bc<br>bc | 12,0,target<br>4,10,target<br>16,0,target |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

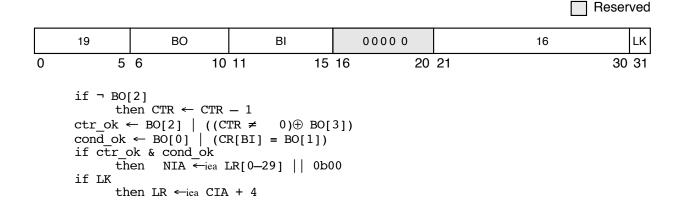

## **bclr***x*

Branch Conditional to Link Register (x'4C00 0020')

| bclr  | BO,BI | (LK = 0) |

|-------|-------|----------|

| bclrl | BO,BI | (LK = 1) |

The BI field specifies the bit in the condition register to be used as the condition of the branch. The BO field is encoded as described in Table 8-8. Additional information about BO field encoding is provided in Section 4.2.4.2, "Conditional Branch Control".

| Table 8-8. | <b>BO Operand</b> | Encodings |

|------------|-------------------|-----------|

|------------|-------------------|-----------|

| во                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                           |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| 0000 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decrement the CTR, then branch if the decremented CTR 0 and the condition is ALSE.    |  |  |

| 0001 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decrement the CTR, then branch if the decremented CTR = 0 and the condition is FALSE. |  |  |

| 001 <i>zy</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Branch if the condition is FALSE.                                                     |  |  |

| 0100 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decrement the CTR, then branch if the decremented CTR 0 and the condition is TRUE.    |  |  |

| 0101 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decrement the CTR, then branch if the decremented CTR = 0 and the condition is TRUE.  |  |  |

| 011 <i>zy</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Branch if the condition is TRUE.                                                      |  |  |

| 1 <i>z</i> 00 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Decrement the CTR, then branch if the decremented CTR 0.                              |  |  |

| 1 <i>z</i> 01 <i>y</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Decrement the CTR, then branch if the decremented CTR = 0.                            |  |  |

| 1 <i>z</i> 1 <i>zz</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Branch always.                                                                        |  |  |

| If the BO field specifies that the CTR is to be decremented, the entire 32-bit CTR is decremented.<br>In this table, <i>z</i> indicates a bit that is ignored.<br><b>Note</b> : The <i>z</i> bits should be cleared, as they may be assigned a meaning in some future version of the<br>PowerPC architecture.<br>The <i>y</i> bit provides a hint about whether a conditional branch is likely to be taken, and may be used by<br>some PowerPC implementations to improve performance. |                                                                                       |  |  |

The branch target address is  $LR[0-29] \parallel 0b00$ .

**bclr**<sub>x</sub>

If LK = 1, then the effective address of the instruction following the branch instruction is placed into the link register.

Other registers altered:

| Affected: Count Register (CTR) |               | (If BO[2]   | =0)  |

|--------------------------------|---------------|-------------|------|

| Affected: Link Register (LR)   |               | (If LK = 1) |      |

| Simplified mnemonics:          |               |             |      |

| bltlr                          | equivalent to | bclr        | 12,0 |

| bnelr cr2                      | equivalent to | bclr        | 4,10 |

| bdnzlr                         | equivalent to | bclr        | 16,0 |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | XL   |

cmp

cmp

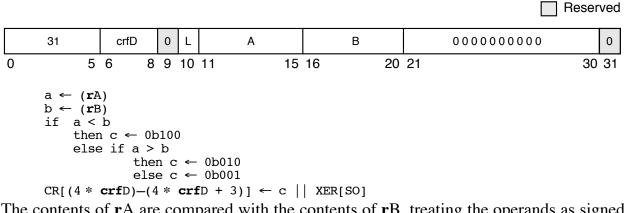

Compare (x'7C00 0000')

cmp

crfD,L,rA,rB

The contents of  $\mathbf{r}A$  are compared with the contents of  $\mathbf{r}B$ , treating the operands as signed integers. The result of the comparison is placed into CR field **crf**D.

**NOTE:** If L = 1, the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand **crf**D): Affected: LT, GT, EQ, SO

| cmpd rA,rB     | equivalent to | cmp | <b>0,1,r</b> A <b>,r</b> B |

|----------------|---------------|-----|----------------------------|

| cmpw cr3,rA,rB | equivalent to | cmp | <b>3,0,r</b> A <b>,r</b> B |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

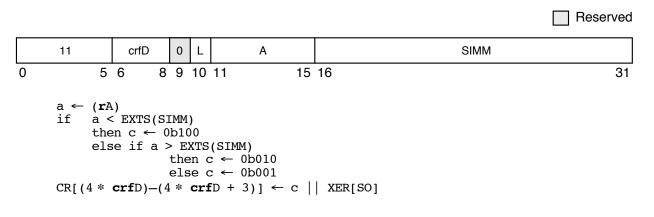

Compare Immediate (x'2C00 0000')

cmpi

cmpi crfD,L,rA,SIMM

The contents of  $\mathbf{r}A$  are compared with the sign-extended value of the SIMM field, treating the operands as signed integers. The result of the comparison is placed into CR field **crfD**.

**NOTE:** If L = 1, the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand **crf**D): Affected: LT, GT, EQ, SO

| cmpdi | rA,value     | equivalent to | cmpi | <b>0,1,r</b> A,value |

|-------|--------------|---------------|------|----------------------|

| cmpwi | cr3,rA,value | equivalent to | cmpi | <b>3,0,r</b> A,value |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

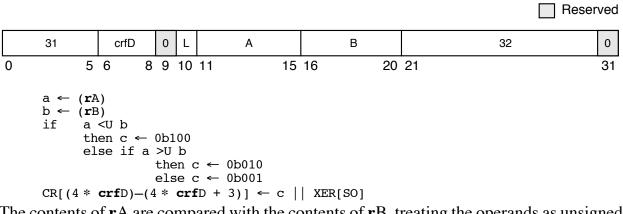

cmpl

cmpl

Compare Logical (x'7C00 0040')

cmpl crfD,L,rA,rB

The contents of  $\mathbf{r}A$  are compared with the contents of  $\mathbf{r}B$ , treating the operands as unsigned integers. The result of the comparison is placed into CR field **crf**D.

**NOTE:** If L = 1, the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand **crf**D): Affected: LT, GT, EQ, SO

| cmpld | rA,rB     | equivalent to | cmpl | <b>0,1,r</b> A <b>,r</b> B |

|-------|-----------|---------------|------|----------------------------|

| cmplw | cr3,rA,rB | equivalent to | cmpl | <b>3,0,r</b> A <b>,r</b> B |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

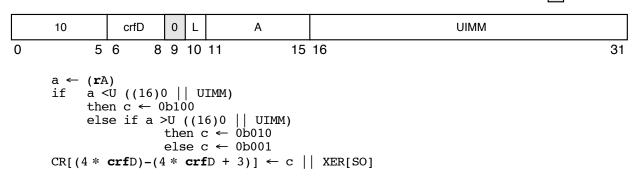

**Compare** Logical Immediate (x'2800 0000')

cmpli crfD,L,rA,UIMM

Reserved

The contents of  $\mathbf{r}A$  are compared with 0x0000 || UIMM, treating the operands as unsigned integers. The result of the comparison is placed into CR field **crf**D.

**NOTE:** If L = 1, the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand **crf**D): Affected: LT, GT, EQ, SO

| cmpldi | r A,value    | equivalent to | cmpli | <b>0,1,r</b> A,value |

|--------|--------------|---------------|-------|----------------------|

| cmplwi | cr3,rA,value | equivalent to | cmpli | <b>3,0,r</b> A,value |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

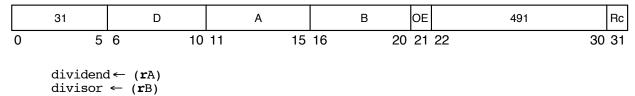

# divw<sub>x</sub>

## **divw***x*

Divide Word (x'7C00 03D6')

| divw<br>divw. | , ,      | (OE = 0 Rc = 0)<br>(OE = 0 Rc = 1) |

|---------------|----------|------------------------------------|

| divwo         | , ,      | (OE = 0 Rc = 1)<br>(OE = 1 Rc = 0) |

| divwo.        | rD,rA,rB | (OE = 1 Rc = 1)                    |

$\mathbf{r}$ D  $\leftarrow$  dividend  $\div$  divisor

The dividend is the contents of **r**A. The divisor is the contents of **r**B. The remainder is not supplied as a result. Both the operands and the quotient are interpreted as signed integers. The quotient is the unique signed integer that satisfies the equation—dividend = (quotient \* divisor) + r where 0 r < ldivisorl (if the dividend is non-negative), and –ldivisorl < r 0 (if the dividend is negative).

If an attempt is made to perform either of the divisions  $-0x8000\_0000 \div -1$  or <anything> ÷ 0, then the contents of **rD** are undefined, as are the contents of the LT, GT, and EQ bits of the CR0 field (if Rc = 1). In this case, if OE = 1 then OV is set.

The 32-bit signed remainder of dividing the contents of **r**A by the contents of **r**B can be computed as follows, except in the case that the contents of  $\mathbf{r}A = -2^{31}$  and the contents of  $\mathbf{r}B = -1$ .

| divw  | rD,rA,rB | $\# \mathbf{r} \mathbf{D} = $ quotient |

|-------|----------|----------------------------------------|

| mullw | rD,rD,rB | <pre># rD = quotient * divisor</pre>   |

| subf  | rD,rD,rA | $\# \mathbf{r} \mathbf{D} = remainder$ |

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (If Rc = 1)

• XER:

Affected: SO, OV

(If OE = 1)

**NOTE:** For more information on condition codes see Section 2.1.3, "Condition Register," and Section 2.1.5, "XER Register."

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | хо   |

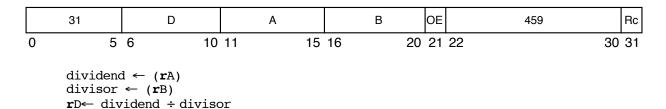

# divwu<sub>x</sub>

| d | iv | W | <b>U</b> x |

|---|----|---|------------|

|---|----|---|------------|

Divide Word Unsigned (x'7C00 0396')

| divwu   | rD,rA,rB | (OE = 0 Rc = 0) |

|---------|----------|-----------------|

| divwu.  | rD,rA,rB | (OE = 0 Rc = 1) |

| divwuo  | rD,rA,rB | (OE = 1 Rc = 0) |

| divwuo. | rD,rA,rB | (OE = 1 Rc = 1) |

The dividend is the contents of  $\mathbf{r}A$ . The divisor is the contents of  $\mathbf{r}B$ . The remainder is not supplied as a result.

Both operands and the quotient are interpreted as unsigned integers, except that if Rc = 1 the first three bits of CR0 field are set by signed comparison of the result to zero. The quotient is the unique unsigned integer that satisfies the equation—dividend = (quotient \* divisor) + r (where 0 r < divisor). If an attempt is made to perform the division—<anything> 0—then the contents of **r**D are undefined as are the contents of the LT, GT, and EQ bits of the CR0 field (if Rc = 1). In this case, if OE = 1 then OV is set.

The 32-bit unsigned remainder of dividing the contents of  $\mathbf{r}A$  by the contents of  $\mathbf{r}B$  can be computed as follows:

| divwu | rD,rA,rB | $\# \mathbf{r} \mathbf{D} = $ quotient |

|-------|----------|----------------------------------------|

| mullw | rD,rD,rB | <pre># rD = quotient * divisor</pre>   |

| subf  | rD,rD,rA | $\# \mathbf{r} \mathbf{D} = remainder$ |

Other registers altered:

- Condition Register (CR0 field): Affected: LT, GT, EQ, SO (If Rc = 1)

- XER: Affected: SO, OV

**NOTE:** For more information on condition codes see Section 2.1.3, "Condition Register," and Section 2.1.5, "XER Register."

(if OE = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | ХО   |

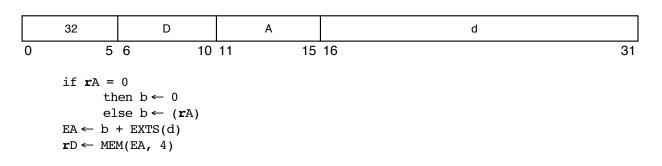

### lwz

Load Word and Zero (x'8000 0000')

rD,d(rA)

lwz

EA is the sum  $(\mathbf{r}A|0) + d$ . The word in memory addressed by EA is loaded into  $\mathbf{r}D$ .

Other registers altered:

• None

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

## lwzu

Load Word and Zero with Update (x'8400 0000')

rD,d(rA) lwzu

EA is the sum  $(\mathbf{r}A) + d$ . The word in memory addressed by EA is loaded into  $\mathbf{r}D$ .

EA is placed into **r**A.

If  $\mathbf{r}A = 0$ , or  $\mathbf{r}A = \mathbf{r}D$ , the instruction form is invalid.

Other registers altered:

• None

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

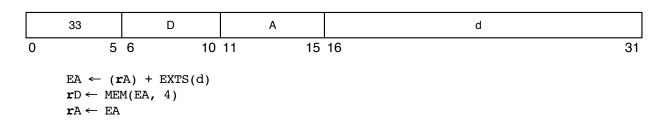

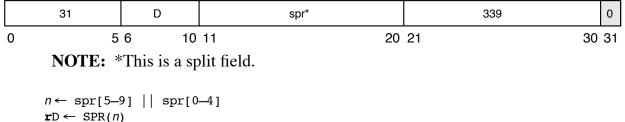

mfspr

mfspr

mfspr

31

D

spr\*

339

0

In the PowerPC UISA, the SPR field denotes a special-purpose register, encoded as shown in Table 8-9. The contents of the designated special purpose register are placed into **r**D

#### Table 8-9. PowerPC UISA SPR Encodings for mfspr

|         | SPR**    | Begister Na |               |  |

|---------|----------|-------------|---------------|--|

| Decimal | spr[5–9] | spr[0–4]    | Register Name |  |

| 1       | 00000    | 00001       | XER           |  |

| 8       | 00000    | 01000       | LR            |  |

| 9       | 00000    | 01001       | CTR           |  |

\*\* Note: The order of the two 5-bit halves of the SPR number is reversed compared with the actual instruction coding.

If the SPR field contains any value other than one of the values shown in Table 8-9 (and the processor is in user mode), one of the following occurs:

- The system illegal instruction error handler is invoked.

- The system supervisor-level instruction error handler is invoked.

- The results are boundedly undefined.

Other registers altered:

• None

| mfxer rD | equivalent to | mfspr rD,1 |

|----------|---------------|------------|

| mflr rD  | equivalent to | mfspr rD,8 |

| mfctr rD | equivalent to | mfspr rD,9 |

In the PowerPC OEA, the SPR field denotes a special-purpose register, encoded as shown in Table 8-10. The contents of the designated SPR are placed into  $\mathbf{r}$ D.

In the PowerPC UISA, the SPR field denotes a special-purpose register, encoded as shown in Table 8-10. If the SPR[0] = 0 (Access type User), the contents of the designated SPR are placed into  $\mathbf{r}$ D.

**NOTE:** For this instruction (**mfspr**), SPR[0] = 1 is supervisor-level, if and only if reading the register. Execution of this instruction specifying a defined and supervisor-level register when MSR[PR] = 1 results in a privileged instruction type program exception.

If MSR[PR] = 1, the only effect of executing an instruction with an SPR number that is not shown in Table 8-10 and has SPR[0] = 1 is to cause a supervisor-level instruction type program exception or an illegal instruction type program exception. For all other cases, MSR[PR] = 0 or SPR[0] = 0. If the SPR field contains any value that is not shown in Table 8-10, either an illegal instruction type program exception occurs or the results are boundedly undefined.

Other registers altered:

None

|         | SPR <sup>1</sup> |          | Register | Access     |  |

|---------|------------------|----------|----------|------------|--|

| Decimal | spr[5–9]         | spr[0–4] | Name     | ALLESS     |  |

| 1       | 00000            | 00001    | XER      | User       |  |

| 8       | 00000            | 01000    | LR       | User       |  |

| 9       | 00000            | 01001    | CTR      | User       |  |

| 18      | 00000            | 10010    | DSISR    | Supervisor |  |

| 19      | 00000            | 10011    | DAR      | Supervisor |  |

| 22      | 00000            | 10110    | DEC      | Supervisor |  |

| 25      | 00000            | 11001    | SDR1     | Supervisor |  |

| 26      | 00000            | 11010    | SRR0     | Supervisor |  |

| 27      | 00000            | 11011    | SRR1     | Supervisor |  |

| 272     | 01000            | 10000    | SPRG0    | Supervisor |  |

| 273     | 01000            | 10001    | SPRG1    | Supervisor |  |

| 274     | 01000            | 10010    | SPRG2    | Supervisor |  |

| 275     | 01000            | 10011    | SPRG3    | Supervisor |  |

| 282     | 01000            | 11010    | EAR      | Supervisor |  |

| 287     | 01000            | 11111    | PVR      | Supervisor |  |

Table 8-10. PowerPC OEA SPR Encodings for mfspr

|         | SPR <sup>1</sup> |          | Register | Access     |  |

|---------|------------------|----------|----------|------------|--|

| Decimal | spr[5–9]         | spr[0–4] | Name     | ALLESS     |  |

| 528     | 10000            | 10000    | IBAT0U   | Supervisor |  |

| 529     | 10000            | 10001    | IBATOL   | Supervisor |  |

| 530     | 10000            | 10010    | IBAT1U   | Supervisor |  |

| 531     | 10000            | 10011    | IBAT1L   | Supervisor |  |

| 532     | 10000            | 10100    | IBAT2U   | Supervisor |  |

| 533     | 10000            | 10101    | IBAT2L   | Supervisor |  |

| 534     | 10000            | 10110    | IBAT3U   | Supervisor |  |

| 535     | 10000            | 10111    | IBAT3L   | Supervisor |  |

| 536     | 10000            | 11000    | DBAT0U   | Supervisor |  |

| 537     | 10000            | 11001    | DBAT0L   | Supervisor |  |

| 538     | 10000            | 11010    | DBAT1U   | Supervisor |  |

| 539     | 10000            | 11011    | DBAT1L   | Supervisor |  |

| 540     | 10000            | 11100    | DBAT2U   | Supervisor |  |

| 541     | 10000            | 11101    | DBAT2L   | Supervisor |  |

| 542     | 10000            | 11110    | DBAT3U   | Supervisor |  |

| 543     | 10000            | 11111    | DBAT3L   | Supervisor |  |

| 1013    | 11111            | 10101    | DABR     | Supervisor |  |

#### Table 8-10. PowerPC OEA SPR Encodings for mfspr (Continued)

<sup>1</sup>Note: The order of the two 5-bit halves of the SPR number is reversed compared with actual instruction coding.

For **mtspr** and **mfspr** instructions, the SPR number coded in assembly language does not appear directly as a 10-bit binary number in the instruction. The number coded is split into two 5-bit halves that are reversed in the instruction, with the high-order five bits appearing in bits 16–20 of the instruction and the low-order five bits in bits 11–15.

**NOTE: mfspr** is supervisor-level only if SPR[0] = 1.

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA/OEA                   | yes*             |                  | XFX  |

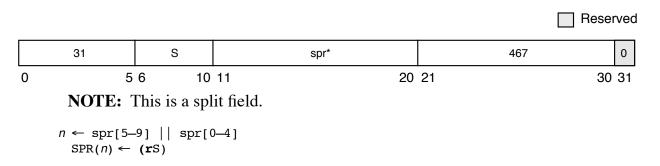

**mtspr** Move to Special-Purpose Register (x'7C00 03A6')

mtspr

SPR,rS

In the PowerPC UISA, the SPR field denotes a special-purpose register, encoded as shown in Table 8-12. The contents of **r**S are placed into the designated special-purpose register.

Table 8-12. PowerPC UISA SPR Encodings for mtspr

|         | SPR**    | Register Name |     |  |

|---------|----------|---------------|-----|--|

| Decimal | spr[5–9] | spr[0–4]      |     |  |

| 1       | 00000    | 00001         | XER |  |

| 8       | 00000    | 01000         | LR  |  |

| 9       | 00000    | 01001         | CTR |  |

\*\* Note: The order of the two 5-bit halves of the SPR number is reversed compared with actual instruction coding.

If the SPR field contains any value other than one of the values shown in Table 8-12, and the processor is operating in user mode, one of the following occurs:

- The system illegal instruction error handler is invoked.

- The system supervisor instruction error handler is invoked.

- The results are boundedly undefined.

Other registers altered:

• See Table 8-12.

Simplified mnemonics:

| mtxer | rD | equivalent to | mtspr | <b>1,r</b> D |

|-------|----|---------------|-------|--------------|

| mtlr  | rD | equivalent to | mtspr | <b>8,r</b> D |

| mtctr | rD | equivalent to | mtspr | <b>9,r</b> D |

mtspr

In the PowerPC OEA, the SPR field denotes a special-purpose register, encoded as shown in Table 8-13. The contents of **rS** are placed into the designated special-purpose register.

In the PowerPC UISA, if the SPR[0]=0 (Access is User) the contents of  $\mathbf{r}S$  are placed into the designated special-purpose register.

For this instruction, SPRs TBL and TBU are treated as separate 32-bit registers; setting one leaves the other unaltered.

The value of SPR[0] = 1 if and only if writing the register is a supervisor-level operation. Execution of this instruction specifying a defined and supervisor-level register when MSR[PR] = 1 results in a privileged instruction type program exception.

If MSR[PR] = 1 then the only effect of executing an instruction with an SPR number that is not shown in Table 8-13 and has SPR[0] = 1 is to cause a privileged instruction type program exception or an illegal instruction type program exception. For all other cases, MSR[PR] = 0 or SPR[0] = 0, if the SPR field contains any value that is not shown in Table 8-13, either an illegal instruction type program exception occurs or the results are boundedly undefined.

Other registers altered:

• See Table 8-13.

|         | SPR <sup>1</sup> |          | Register | Access     |

|---------|------------------|----------|----------|------------|

| Decimal | spr[5–9]         | spr[0–4] | Name     | ALLESS     |

| 1       | 00000            | 00001    | XER      | User       |

| 8       | 00000            | 01000    | LR       | User       |

| 9       | 00000            | 01001    | CTR      | User       |

| 18      | 00000            | 10010    | DSISR    | Supervisor |

| 19      | 00000            | 10011    | DAR      | Supervisor |

| 22      | 00000            | 10110    | DEC      | Supervisor |

| 25      | 00000            | 11001    | SDR1     | Supervisor |

| 26      | 00000            | 11010    | SRR0     | Supervisor |

| 27      | 00000            | 11011    | SRR1     | Supervisor |

| 272     | 01000            | 10000    | SPRG0    | Supervisor |

| 273     | 01000            | 10001    | SPRG1    | Supervisor |

| 274     | 01000            | 10010    | SPRG2    | Supervisor |

| 275     | 01000            | 10011    | SPRG3    | Supervisor |

| 282     | 01000            | 11010    | EAR      | Supervisor |

Table 8-13. PowerPC OEA SPR Encodings for mtspr

8

|         | SPR <sup>1</sup> |          | Register |            |

|---------|------------------|----------|----------|------------|

| Decimal | spr[5–9]         | spr[0–4] | Name     | Access     |

| 284     | 01000            | 11100    | TBL      | Supervisor |

| 285     | 01000            | 11101    | TBU      | Supervisor |

| 528     | 10000            | 10000    | IBATOU   | Supervisor |

| 529     | 10000            | 10001    | IBATOL   | Supervisor |

| 530     | 10000            | 10010    | IBAT1U   | Supervisor |

| 531     | 10000            | 10011    | IBAT1L   | Supervisor |

| 532     | 10000            | 10100    | IBAT2U   | Supervisor |

| 533     | 10000            | 10101    | IBAT2L   | Supervisor |

| 534     | 10000            | 10110    | IBAT3U   | Supervisor |

| 535     | 10000            | 10111    | IBAT3L   | Supervisor |

| 536     | 10000            | 11000    | DBAT0U   | Supervisor |

| 537     | 10000            | 11001    | DBAT0L   | Supervisor |

| 538     | 10000            | 11010    | DBAT1U   | Supervisor |

| 539     | 10000            | 11011    | DBAT1L   | Supervisor |

| 540     | 10000            | 11100    | DBAT2U   | Supervisor |

| 541     | 10000            | 11101    | DBAT2L   | Supervisor |

| 542     | 10000            | 11110    | DBAT3U   | Supervisor |

| 543     | 10000            | 11111    | DBAT3L   | Supervisor |

| 1013    | 11111            | 10101    | DABR     | Supervisor |

#### Table 8-13. PowerPC OEA SPR Encodings for mtspr (Continued)

<sup>1</sup>Note: The order of the two 5-bit halves of the SPR number is reversed. For **mtspr** and **mfspr** instructions, the SPR number coded in assembly language does not appear directly as a 10-bit binary number in the instruction. The number coded is split into two 5-bit halves that are reversed in the instruction, with the high-order five bits appearing in bits 16–20 of the instruction and the low-order five bits in bits 11–15.

**NOTE: mtspr** is supervisor-level only if SPR[0] = 1.

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA/OEA                   | yes*             |                  | XFX  |

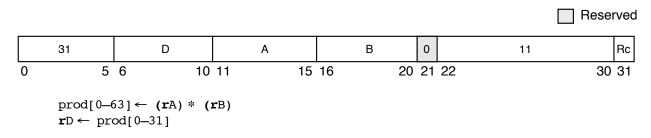

### mulhw<sub>x</sub>

## mulhw<sub>x</sub>

Multiply High Word (x'7C00 0096')

| mulhw  | rD,rA,rB | (Rc = 0) |

|--------|----------|----------|

| mulhw. | rD,rA,rB | (Rc = 1) |

The 64-bit product is formed from the contents of  $\mathbf{r}A$  and  $\mathbf{r}B$ . The high-order 32 bits of the 64-bit product of the operands are placed into  $\mathbf{r}D$ .

Both the operands and the product are interpreted as signed integers.

This instruction may execute faster on some implementations if  $\mathbf{r}B$  contains the operand having the smaller absolute value.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (If Rc = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | ХО   |

## **mulhwu***x*

# mulhwu*x*

Multiply High Word Unsigned (x'7C00 0016')

| mulhwu  | rD,rA,rB | (Rc = 0) |

|---------|----------|----------|

| mulhwu. | rD,rA,rB | (Rc = 1) |

The 32-bit operands are the contents of **r**A and **r**B. The high-order 32 bits of the 64-bit product of the operands are placed into **r**D.

Both the operands and the product are interpreted as unsigned integers, except that if Rc = 1 the first three bits of CR0 field are set by signed comparison of the result to zero.

This instruction may execute faster on some implementations if  $\mathbf{r}B$  contains the operand having the smaller absolute value.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (If Rc = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | хо   |

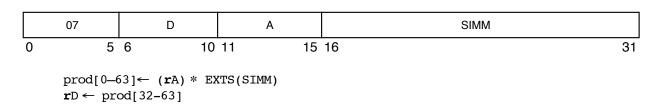

mulli

mulli

Multiply Low Immediate (x'1C00 0000')

mulli rD,rA,SIMM

The first operand is  $(\mathbf{r}A)$ . The second operand is the sign-extended value of the SIMM field. The low-order 32-bits of the 64-bit product of the operands are placed into  $\mathbf{r}D$ .

Both the operands and the product are interpreted as signed integers. The low-order 32-bits of the product are calculated independently of whether the operands are treated as signed or unsigned 32-bit integers.

This instruction can be used with **mulhd***x* or **mulhw***x* to calculate a full 64-bit product.

Other registers altered:

• None

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

8

## mullw<sub>x</sub>

# mullw<sub>x</sub>

Multiply Low Word (x'7C00 01D6')

| rD,rA,rB | (OE = 0 Rc = 0)      |

|----------|----------------------|

| rD,rA,rB | (OE = 0 Rc = 1)      |

| rD,rA,rB | (OE = 1 Rc = 0)      |

| rD,rA,rB | (OE = 1 Rc = 1)      |

|          | rD,rA,rB<br>rD,rA,rB |

|   | 31 | D                                                                                                           | А            | В     | OE    | 235 | Rc |

|---|----|-------------------------------------------------------------------------------------------------------------|--------------|-------|-------|-----|----|

| 0 |    | $6 \qquad 10$ $53] \leftarrow (\mathbf{r}A) * (\mathbf{r}A)$ $53] \leftarrow (\mathbf{r}A) + (\mathbf{r}A)$ | 11 15<br>rB) | 16 20 | 21 22 | 30  | 31 |

The 32-bit operands are the contents of  $\mathbf{r}A$  and  $\mathbf{r}B$ . The low-order 32-bits of the 64-bit product ( $\mathbf{r}A$ ) \* ( $\mathbf{r}B$ ) are placed into  $\mathbf{r}D$ .

The low-order 32-bits of the product are independent of whether the operands are regarded as signed or unsigned 32-bit integers.

If OE = 1, then OV is set if the product cannot be represented in 32 bits. Both the operands and the product are interpreted as signed integers.

This instruction can be used with **mulhw***x* to calculate a full 64-bit product.

**NOTE:** This instruction may execute faster on some implementations if **r**B contains the operand having the smaller absolute value.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (If Rc = 1)

**NOTE:** CR0 field may not reflect the infinitely precise result if overflow occurs (see next).

• XER:

Affected: SO, OV (If OE = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | хо   |

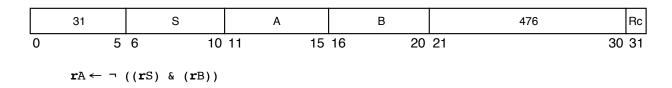

**nand***x* NAND (x'7C00 03B8')

# nand*x*

| nand  | rA,rS,rB | (Rc = 0) |

|-------|----------|----------|

| nand. | rA,rS,rB | (Rc = 1) |

The contents of  $\mathbf{r}S$  are ANDed with the contents of  $\mathbf{r}B$  and the complemented result is placed into  $\mathbf{r}A$ .

**nand** with  $\mathbf{rS} = \mathbf{rB}$  can be used to obtain the one's complement.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (If Rc = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

### negx

Negate (x'7C00 00D0')

| neg   | rD,rA | (OE = 0 Rc = 0) |

|-------|-------|-----------------|

| neg.  | rD,rA | (OE = 0 Rc = 1) |

| nego  | rD,rA | (OE = 1 Rc = 0) |

| nego. | rD,rA | (OE = 1 Rc = 1) |

Reserved

|   | 31   | D                 |       | А  |    | 00000 | OE | 104 |    | Rc |

|---|------|-------------------|-------|----|----|-------|----|-----|----|----|

| 0 | 5    | 6                 | 10 11 | 15 | 16 | 20    | 21 | 22  | 30 | 31 |

|   | rD←¬ | ( <b>r</b> A) + 1 |       |    |    |       |    |     |    |    |

The value 1 is added to the one's complement of the value in  $\mathbf{r}A$ , and the resulting two's complement is placed into  $\mathbf{r}D$ .

If **r**A contains the most negative 32-bit number ( $0x8000_{0000}$ ), the result is the most negative number and, if OE = 1, OV is set.

Other registers altered:

- Condition Register (CR0 field): Affected: LT, GT, EQ, SO (If Rc = 1)

- XER: Affected: SO OV (If OE = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | ХО   |

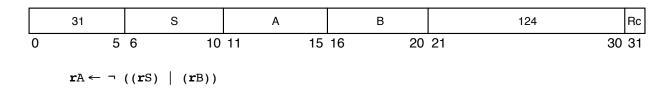

**NOR** (x'7C00 00F8')

| nor  | rA,rS,rB | (Rc = 0) |

|------|----------|----------|

| nor. | rA,rS,rB | (Rc = 1) |

The contents of  $\mathbf{r}S$  are ORed with the contents of  $\mathbf{r}B$  and the complemented result is placed into  $\mathbf{r}A$ .

**nor** with  $\mathbf{rS} = \mathbf{rB}$  can be used to obtain the one's complement.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (If Rc = 1) Simplified mnemonics:

| not | rD,rS | equivalent to | nor | rA,rS,rS |

|-----|-------|---------------|-----|----------|

|-----|-------|---------------|-----|----------|

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

8

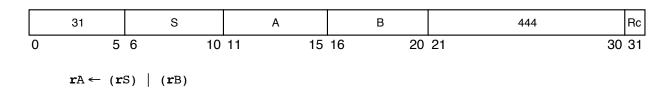

**Oľ***X* OR (x'7C00 0378')

8

| or  | rA,rS,rB | (Rc = 0) |

|-----|----------|----------|

| or. | rA,rS,rB | (Rc = 1) |

The contents of  $\mathbf{r}S$  are ORed with the contents of  $\mathbf{r}B$  and the result is placed into  $\mathbf{r}A$ .

The simplified mnemonic **mr** (shown below) demonstrates the use of the **or** instruction to move register contents.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (If Rc = 1)

| mr | rA,rS | equivalent to | or | rA,rS,rS |

|----|-------|---------------|----|----------|

|----|-------|---------------|----|----------|

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

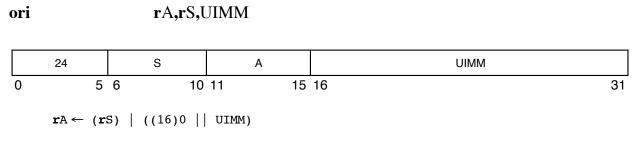

ori

OR Immediate (x'6000 0000')

The contents of  $\mathbf{rS}$  are ORed with  $0x0000 \parallel \text{UIMM}$  and the result is placed into  $\mathbf{rA}$ .

The preferred no-op (an instruction that does nothing) is **ori 0,0,0**.

Other registers altered:

• None

| nop | equivalent to | ori | 0,0,0 |  |

|-----|---------------|-----|-------|--|

|-----|---------------|-----|-------|--|

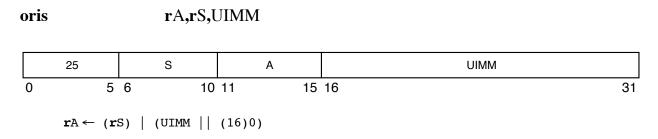

oris

OR Immediate Shifted (x'6400 0000')

The contents of **r**S are ORed with UIMM  $\parallel 0x0000$  and the result is placed into **r**A. Other registers altered:

• None

8

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

# rlwimi*x*

# **rlwimi***x*

Rotate Left Word Immediate then Mask Insert (x'5000 0000')

| rlwimi  | rA,rS,SH,MB,ME | (Rc = 0) |

|---------|----------------|----------|

| rlwimi. | rA,rS,SH,MB,ME | (Rc = 1) |

|   | 20 | S                                                               | А     | SH    | МВ    | ME    | Rc |

|---|----|-----------------------------------------------------------------|-------|-------|-------|-------|----|

| 0 | 5  | 6 10                                                            | 11 15 | 16 20 | 21 25 | 26 30 | 31 |

|   |    | L( <b>r</b> S, <i>n</i> )<br>K(MB, ME)<br>& m)   ( <b>r</b> A & | ⊐ m)  |       |       |       |    |

The contents of  $\mathbf{rS}$  are rotated left the number of bits specified by operand SH. A mask is generated having 1 bits from bit MB through bit ME and 0 bits elsewhere. The rotated data is inserted into  $\mathbf{rA}$  under control of the generated mask.

- **NOTE: rlwimi** can be used to copy a bit field of any length from register **r**S into the contents of **r**A. This field can start from any bit position in **r**S and be placed into any position in **r**A. The length of the field can range from 0 to 32 bits. The remaining bits in register **r**A remain unchanged:

- To copy byte\_0 (bits 0-7) from rS into byte\_3 (bits 24-31) of rA, set SH = 8, MB = 24, and ME = 31.

- In general, to copy an *n*-bit field that starts in bit position b in register rS into register rA starting a bit position c: set  $SH = 32 c + b \mod(32)$ , set MB = c, and set  $ME = (c + n) 1 \mod(32)$ .

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (if Rc = 1)

Simplified mnemonics:

inslwi rA,rS,n,b equivalent to rlwimirA,rS,32 - b,b,b + n - 1insrwi rA,rS,n,b (n > 0) equivalent to rlwimirA,rS,32 - (b + n), b, (b + n) - 1

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | М    |

## **rlwinm***x*

## rlwinm*x*

Rotate Left Word Immediate then AND with Mask (x'5400 0000')

| rlwinm  | rA,rS,SH,MB,ME | (Rc = 0) |

|---------|----------------|----------|

| rlwinm. | rA,rS,SH,MB,ME | (Rc = 1) |

|   | 21                                                                                       | S         | A     | SH    | MB    | ME    | Rc |

|---|------------------------------------------------------------------------------------------|-----------|-------|-------|-------|-------|----|

| 0 | 5                                                                                        | 6 10      | 11 15 | 16 20 | 21 25 | 26 30 | 31 |

|   | $n \leftarrow SH$<br>$r \leftarrow ROTI$<br>$m \leftarrow MASH$<br>$rA \leftarrow r \in$ | K(MB, ME) |       |       |       |       |    |

The contents of  $\mathbf{rS}$  are rotated left the number of bits specified by operand SH. A mask is generated having 1 bits from bit MB through bit ME and 0 bits elsewhere. The rotated data is ANDed with the generated mask and the result is placed into  $\mathbf{rA}$ .

- **NOTE: rlwinm** can be used to extract, rotate, shift, and clear bit fields using the methods shown below:

- To extract an *n*-bit field, that starts at bit position *b* in **r**S, right-justified into **r**A (clearing the remaining 32 *n* bits of **r**A), set SH = b + n, MB = 32 n, and ME = 31.

- To extract an *n*-bit field, that starts at bit position *b* in **r**S, left-justified into **r**A (clearing the remaining 32 n bits of **r**A), set SH = *b*, MB = 0, and ME = n 1.

- To rotate the contents of a register left (or right) by *n* bits, set SH = n (32 n), MB = 0, and ME = 31.

- To shift the contents of a register right by *n* bits, by setting SH = 32 n, MB = n, and ME = 31. It can be used to clear the high-order *b* bits of a register and then shift the result left by *n* bits by setting SH = n, MB = b n and ME = 31 n.

- To clear the low-order *n* bits of a register, by setting SH = 0, MB = 0, and ME = 31 n.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (if Rc = 1) Simplified mnemonics:

| extlwi rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0)   | equivalent to | rlwinm rA,rS,b,0, <i>n</i> – 1                              |

|-----------------------------------------------------|---------------|-------------------------------------------------------------|

| extrwi rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0)   | equivalent to | rlwinm rA,rS,b + <i>n</i> ,32 – <i>n</i> ,31                |

| rotlwi rA,rS, <i>n</i>                              | equivalent to | rlwinm rA,rS, <i>n</i> ,0,31                                |

| rotrwi rA,rS, $n$                                   | equivalent to | rlwinm rA,rS, <b>32</b> – <i>n</i> , <b>0,31</b>            |

| slwi rA,rS, $n$ ( $n < 32$ )                        | equivalent to | rlwinm rA,rS, <i>n</i> , <b>0</b> ,31– <i>n</i>             |

| <b>srwi rA,rS,</b> $n$ ( $n < 32$ )                 | equivalent to | rlwinm rA,rS,32 – <i>n,n</i> ,31                            |

| <b>clrlwi rA,rS,</b> $n$ ( $n < 32$ )               | equivalent to | rlwinm rA,rS,0, <i>n</i> ,31                                |

| <b>clrrwi rA,rS,</b> $n$ ( $n < 32$ )               | equivalent to | rlwinm rA,rS,0,0,31 – <i>n</i>                              |

| <b>clrlslwi rA,rS,</b> $b$ , $n$ ( $n \le b < 32$ ) | equivalent to | rlwinm rA,rS, <i>n</i> , <i>b</i> – <i>n</i> ,31 – <i>n</i> |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | М    |

## **rlwnm***x*

## **rlwnm***x*

Rotate Left Word then AND with Mask (x'5C00 0000')

| rlwnm  | rA,rS,rB,MB,ME | (Rc = 0) |

|--------|----------------|----------|

| rlwnm. | rA,rS,rB,MB,ME | (Rc = 1) |

|   | 23                                                                                                                                                                                                                                 | S                                      | А     | В     | MB    | ME    | Rc |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|-------|-------|-------|----|

| 0 | 5                                                                                                                                                                                                                                  | 6 10                                   | 11 15 | 16 20 | 21 25 | 26 30 | 31 |

|   | $n \leftarrow \mathbf{r} \mathbb{B}[2]$ $\mathbf{r} \leftarrow \mathbb{R} \mathbb{O} \mathbb{T}]$ $\mathbf{m} \leftarrow \mathbb{M} \mathbb{A} \mathbb{S} \mathbb{F}$ $\mathbf{r} \mathbb{A} \leftarrow \mathbf{r} \in \mathbb{C}$ | L( <b>r</b> S, <i>n</i> )<br>K(MB, ME) |       |       |       |       |    |

The contents of  $\mathbf{rS}$  are rotated left the number of bits specified by the low-order five bits of  $\mathbf{rB}$ . A mask is generated having 1 bits from bit MB through bit ME and 0 bits elsewhere. The rotated data is ANDed with the generated mask and the result is placed into  $\mathbf{rA}$ .

**NOTE: rlwnm** can be used to extract and rotate bit fields using the methods shown as follows:

- To extract an *n*-bit field, that starts at variable bit position *b* in **r**S, right-justified into **r**A (clearing the remaining 32 n bits of **r**A), by setting the low-order five bits of **r**B to b + n, MB = 32 n, and ME = 31.

- To extract an *n*-bit field, that starts at variable bit position *b* in **r**S, left-justified into **r**A (clearing the remaining 32 n bits of **r**A), by setting the low-order five bits of **r**B to *b*, MB = 0, and ME = n 1.

- To rotate the contents of a register left (or right) by *n* bits, by setting the low-order five bits of **r**B to n(32 n), MB = 0, and ME = 31.

Other registers altered:

- Condition Register (CR0 field):

- Affected: LT, GT, EQ, SO (if Rc = 1)

Simplified mnemonics:

| rotlw rA,rS,rB equivalent to rlwn | n rA,rS,rB, <b>0,31</b> |

|-----------------------------------|-------------------------|

|-----------------------------------|-------------------------|

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | М    |

8

## slw*x*

slw*x*

Shift Left Word (x'7C00 0030')

| slw<br>slw. | rA,rS,rB       (Rc = 0) $rA,rS,rB$ (Rc = 1) |                                                     |    |            |    |    |    |    |    |    |    |

|-------------|---------------------------------------------|-----------------------------------------------------|----|------------|----|----|----|----|----|----|----|

|             | 31                                          | S                                                   |    | А          |    |    | В  |    | 24 |    | Rc |

| 0           | 5                                           | 6                                                   | 10 | 11         | 15 | 16 | 20 | 21 |    | 30 | 31 |

|             | if <b>r</b> B[20<br>th                      | L( <b>r</b> S, n)<br>6] = 0<br>en m ← M<br>se m ← M |    | ), 31 — n) |    |    |    |    |    |    |    |

The contents of  $\mathbf{rS}$  are shifted left the number of bits specified by the low-order five bits of  $\mathbf{rB}$ . Bits shifted out of position 0 are lost. Zeros are supplied to the vacated positions on the right. The 32-bit result is placed into  $\mathbf{rA}$ . However, shift amounts from 32 to 63 give a zero result.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (if Rc = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

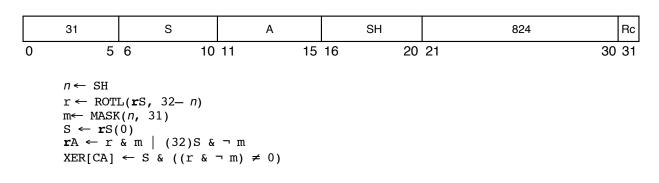

### srawx

### sraw<sub>x</sub>

Shift Right Algebraic Word (x'7C00 0630')

| sraw  | rA,rS,rB | (Rc = 0) |

|-------|----------|----------|

| sraw. | rA,rS,rB | (Rc = 1) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 | S |      | А |    |    | В  |    | 792 |    | Rc |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|------|---|----|----|----|----|-----|----|----|

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5  | 6 | 10 1 | 1 | 15 | 16 | 20 | 21 |     | 30 | 31 |

| $n \leftarrow \mathbf{r} \mathbb{B}[27-31]$ $r \leftarrow \mathbb{ROTL}(\mathbf{r} \mathbb{S}, 32-n)$ if $\mathbf{r} \mathbb{B}[26] = 0$ $\text{then } \mathbf{m} \leftarrow \mathbb{MASK}(n, 31)$ $\text{else } \mathbf{m} \leftarrow (32)0$ $\mathbf{S} \leftarrow \mathbf{r} \mathbb{S}(0)$ $\mathbf{r} \mathbb{A} \leftarrow \mathbf{r} \& \mathbf{m} \mid (32)\mathbb{S} \& \neg \mathbf{m}$ $\text{XER}[CA] \leftarrow \mathbb{S} \& ((\mathbf{r} \& \neg \mathbf{m}) \neq 0)$ |    |   |      |   |    |    |    |    |     |    |    |

The contents of **r**S are shifted right the number of bits specified by the low-order five bits of **r**B (shift amounts between 0-31). Bits shifted out of position 31 are lost. Bit 0 of **r**S is replicated to fill the vacated positions on the left. The 32-bit result is placed into **r**A. XER[CA] is set if **r**S contains a negative number and any 1 bits are shifted out of position 31; otherwise XER[CA] is cleared. A shift amount of zero causes **r**A to receive the 32 bits of **r**S, and XER[CA] to be cleared. However, shift amounts from 32 to 63 give a result of 32 sign bits, and cause XER[CA] to receive the sign bit of **r**S.

**NOTE:** The **sraw** instruction, followed by **addze**, can be used to divide quickly by  $2^n$ .

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO

(if Rc = 1)

• XER:

Affected: CA

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

## srawix

srawi*x*

Shift Right Algebraic Word Immediate (x'7C00 0670')

| srawi  | rA,rS,SH | (Rc=0)   |

|--------|----------|----------|

| srawi. | rA,rS,SH | (Rc = 1) |

The contents of  $\mathbf{rS}$  are shifted right SH bits. Bits shifted out of position 31 are lost. Bit 0 of  $\mathbf{rS}$  is replicated to fill the vacated positions on the left. The result is placed into  $\mathbf{rA}$ . XER[CA] is set if the 32 bits of  $\mathbf{rS}$  contain a negative number and any 1 bits are shifted out of position 31; otherwise XER[CA] is cleared. A shift amount of zero causes  $\mathbf{rA}$  to receive the value of  $\mathbf{rS}$ , and XER[CA] to be cleared.

**NOTE:** The **srawi** instruction, followed by **addze**, can be used to divide quickly by  $2^n$ .

Other registers altered:

- Condition Register (CR0 field): Affected: LT, GT, EQ, SO (if Rc = 1)

- XER:

Affected: CA

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

8

### **Srw***x*

### **Srw***x*

Shift Right Word (x'7C00 0430')

| srw<br>srw. |                                                                                                        |                                                                                          | ,rS,rB<br>,rS,rB | $(\mathbf{Rc} = 0)$ $(\mathbf{Rc} = 1)$ |     |       |

|-------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|-----------------------------------------|-----|-------|

|             | 31                                                                                                     | S                                                                                        | А                | В                                       | 536 | Rc    |

| 0           | $n \leftarrow \mathbf{r} \mathbb{B}[2]$<br>$r \leftarrow ROTI$<br>if $\mathbf{r} \mathbb{B}[20]$<br>th | 27-31]<br>L( <b>r</b> S, 32- <i>n</i> )<br>5] = 0<br>en m← MASK( <i>n</i><br>se m← (32)0 |                  | 16 20                                   | 21  | 30 31 |

The contents of  $\mathbf{rS}$  are shifted right the number of bits specified by the low-order five bits of  $\mathbf{rB}$  (shift amounts between 0-31). Bits shifted out of position 31 are lost. Zeros are supplied to the vacated positions on the left. The 32-bit result is placed into  $\mathbf{rA}$ . However, shift amounts from 32 to 63 give a zero result.

Other registers altered:

• Condition Register (CR0 field): Affected: LT, GT, EQ, SO (if Rc = 1)

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | Х    |

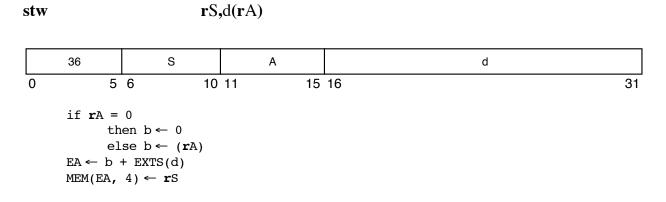

## stw

Store Word (x'9000 0000')

EA is the sum  $(\mathbf{r}A|0) + d$ . The contents of  $\mathbf{r}S$  are stored into the word in memory addressed by EA.

Other registers altered:

• None

|   | c | 9 | 1 |  |

|---|---|---|---|--|

| 7 | 2 |   | Т |  |

| L |   |   | v |  |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | D    |

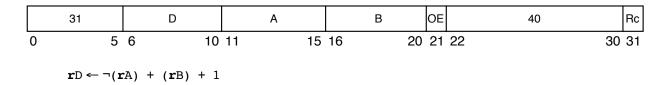

## subf*x*

subf<sub>x</sub>

Subtract From (x'7C00 0050')

| subf   | rD,rA,rB | (OE = 0 Rc = 0) |

|--------|----------|-----------------|

| subf.  | rD,rA,rB | (OE = 0 Rc = 1) |

| subfo  | rD,rA,rB | (OE = 1 Rc = 0) |

| subfo. | rD,rA,rB | (OE = 1 Rc = 1) |

The sum  $\neg$  (**r**A) + (**r**B) + 1 is placed into **r**D. (equivlent to (rB)--(**r**A))

The **subf** instruction is preferred for subtraction because it sets few status bits.

Other registers altered:

| sub  | rD,rA,rB            | equivalent to | subf         | rD,rB,rA |

|------|---------------------|---------------|--------------|----------|

| Simp | lified mnemonics:   |               |              |          |

|      | Affected: SO, OV    |               | (if $OE =$   | 1)       |

| •    | XER:                |               |              |          |

|      | Affected: LT, GT, E | EQ, SO        | (if $Rc = 1$ | )        |

| ٠    | Condition Register  | (CR0 field):  |              |          |

| PowerPC Architecture Level | Supervisor Level | PowerPC Optional | Form |

|----------------------------|------------------|------------------|------|

| UISA                       |                  |                  | ХО   |

## **Appendix F. Simplified Mnemonics**

This appendix is provided in order to simplify the writing and comprehension of assembler language programs. Included are a set of simplified mnemonics and symbols that define the simple shorthand used for the most frequently-used forms of branch conditional, compare, trap, rotate and shift, and certain other instructions.

### F.1 Symbols

The symbols in Table F-1 are defined for use in instructions (basic or simplified mnemonics) that specify a condition register (CR) field or a bit in the CR.

| Symbol | Value | Bit Field<br>Range | Description                                                                         |

|--------|-------|--------------------|-------------------------------------------------------------------------------------|

| lt     | 0     | _                  | Less than. Identifies a bit number within a CR field.                               |

| gt     | 1     | _                  | Greater than. Identifies a bit number within a CR field.                            |

| eq     | 2     | _                  | Equal. Identifies a bit number within a CR field.                                   |

| so     | 3     | _                  | Summary overflow. Identifies a bit number within a CR field.                        |

| un     | 3     | _                  | Unordered (after floating-point comparison). Identifies a bit number in a CR field. |

| cr0    | 0     | 0–3                | CR0 field                                                                           |

| cr1    | 1     | 4–7                | CR1 field                                                                           |

| cr2    | 2     | 8–11               | CR2 field                                                                           |

| cr3    | 3     | 12–15              | CR3 field                                                                           |

| cr4    | 4     | 16–19              | CR4 field                                                                           |

| cr5    | 5     | 20–23              | CR5 field                                                                           |

| cr6    | 6     | 24–27              | CR6 field                                                                           |

| cr7    | 7     | 28–31              | CR7 field                                                                           |

Table F-1. Condition Register Bit and Identification Symbol Descriptions

**Note:** To identify a CR bit, an expression in which a CR field symbol is multiplied by 4 and then added to a bit-numberwithin-CR-field symbol can be used.

**NOTE:** The architecture specification refers to simplified mnemonics as extended mnemonics.

The simplified mnemonics in Section F.5.2, "Basic Branch Mnemonics," and Section F.6, "Simplified Mnemonics for Condition Register Logical Instructions," require identification of a CR bit—if one of the CR field symbols is used, it must be multiplied by 4 and added to a bit-number-within-CR-field (value in the range of 0–3, explicit or symbolic).

The simplified mnemonics in Section F.5.3, "Branch Mnemonics Incorporating Conditions," and Section F.3, "Simplified Mnemonics for Compare Instructions," require identification of a CR field—if one of the CR field symbols is used, it must not be multiplied by 4.

Also, for the simplified mnemonics in Section F.5.3, "Branch Mnemonics Incorporating Conditions," the bit number within the CR field is part of the simplified mnemonic. The CR field is identified, and the assembler does the multiplication and addition required to produce a CR bit number for the BI field of the underlying basic mnemonic.

## F.2 Simplified Mnemonics for Subtract Instructions

This section discusses simplified mnemonics for the subtract instructions.

#### F.2.1 Subtract Immediate

Although there is no subtract immediate instruction, its effect can be achieved by using an add immediate instruction with the immediate operand negated. Simplified mnemonics are provided that include this negation, making the intent of the computation more clear.

| subi rD,rA,value   | (equivalent to | addi rD,rA,–value)   |

|--------------------|----------------|----------------------|

| subis rD,rA,value  | (equivalent to | addis rD,rA,-value)  |

| subic rD,rA,value  | (equivalent to | addic rD,rA,-value)  |

| subic. rD,rA,value | (equivalent to | addic. rD,rA,-value) |

#### F.2.2 Subtract

The subtract from instructions subtract the second operand  $(\mathbf{r}A)$  from the third  $(\mathbf{r}B)$ . Simplified mnemonics are provided that use the more normal order in which the third operand is subtracted from the second. Both these mnemonics can be coded with an **o** suffix and/or dot (.) suffix to cause the OE and/or Rc bit to be set in the underlying instruction.

| sub rD,rA,rB  | (equivalent to | subf rD,rB,rA)             |

|---------------|----------------|----------------------------|

| subc rD,rA,rB | (equivalent to | <pre>subfc rD,rB,rA)</pre> |

F

## F.3 Simplified Mnemonics for Compare Instructions

The **crf**D field can be omitted if the result of the comparison is to be placed into the CR0 field. Otherwise, the target CR field must be specified as the first operand. One of the CR field symbols defined in Section F.1, "Symbols," can be used for this operand.

**NOTE:** The basic compare mnemonics of PowerPC are the same as those of POWER, but the POWER instructions have three operands whereas the PowerPC instructions have four. The assembler recognizes a basic compare mnemonic with the three operands as the POWER form, and generates the instruction with L = 0. The **crf**D field can normally be omitted when the CR0 field is the target.

#### F.3.1 Word Comparisons

The instructions listed in Table F-2 are simplified mnemonics that should be supported by assemblers for all PowerPC implementations.

| Operation                      | Simplified Mnemonic | Equivalent to:       |