- AC Types Feature 1.5-V to 5.5-V Operation and Balanced Noise Immunity at 30% of the **Supply Voltage**

- Speed of Bipolar F, AS, and S, With **Significantly Reduced Power Consumption**

- **Balanced Propagation Delays**

- ±24-mA Output Drive Current - Fanout to 15 F Devices

- **SCR-Latchup-Resistant CMOS Process and Circuit Design**

- **Exceeds 2-kV ESD Protection Per** MIL-STD-883, Method 3015

#### CD54AC04 . . . F PACKAGE CD74AC04...E OR M PACKAGE (TOP VIEW) 14 🛮 V<sub>CC</sub> 1A L 1Y Π 13 🛮 6A 6Y 2A 🛮 12 3 2Y 🛮 4 11 🛮 5A 3A 🛛 5 10 [] 5Y зү Г 9 **1** 4A 6 GND 7 8 4Y

### description

The 'AC04 devices contain six independent inverters. The devices perform the Boolean function  $Y = \overline{A}$ .

#### **ORDERING INFORMATION**

| TA             | PACKAGE† |               | ORDERABLE PART NUMBER | TOP-SIDE<br>MARKING |

|----------------|----------|---------------|-----------------------|---------------------|

|                | PDIP – E | Tube          | CD74AC04E             | CD74AC04E           |

| –55°C to 125°C | SOIC - M | Tube          | CD74AC04M             | AC04M               |

|                |          | Tape and reel | CD74AC04M96           | AC04IVI             |

|                | CDIP – F | Tube          | CD54AC04F3A           | CD54AC04F3A         |

<sup>†</sup>Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

#### **FUNCTION TABLE** (each inverter)

| INPUT<br>A | OUTPUT<br>Y |

|------------|-------------|

| Н          | L           |

| L          | Н           |

logic diagram, each inverter (positive logic)

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# CD54AC08, CD74AC08 QUADRUPLE 2-INPUT POSITIVE-AND GATES

SCHS307C - JANUARY 2001 - REVISED JUNE 2002

- AC Types Feature 1.5-V to 5.5-V Operation and Balanced Noise Immunity at 30% of the Supply Voltage

- Speed of Bipolar F, AS, and S, With Significantly Reduced Power Consumption

- Balanced Propagation Delays

- Buffered Inputs

- ±24-mA Output Drive Current

- Fanout to 15 F Devices

- SCR-Latchup-Resistant CMOS Process and Circuit Design

- Exceeds 2-kV ESD Protection Per MIL-STD-883, Method 3015

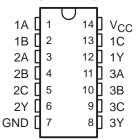

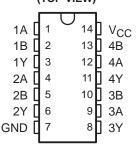

#### CD54AC08...F PACKAGE CD74AC08...E OR M PACKAGE (TOP VIEW) 14 🛛 V<sub>CC</sub> 1A 13 **[**] 4B 1В П 1Y [] 3 12 🛮 4A 2A 🛮 4 11 🛮 4Y 2B 🛮 5 10 T 3B 2Y [ 6 9 🛮 3A GND [] 7 8 🛮 3Y

### description

The 'AC08 devices are quadruple 2-input positive-AND gates. These devices perform the Boolean function  $Y = A \bullet B$  or  $Y = \overline{A + B}$  in positive logic.

#### ORDERING INFORMATION

| TA | PACKAGE <sup>†</sup> |               | ORDERABLE PART NUMBER | TOP-SIDE<br>MARKING |

|----|----------------------|---------------|-----------------------|---------------------|

| 1  | PDIP – E             | Tube          | CD74AC08E             | CD74AC08E           |

|    | SOIC - M             | Tube          | CD74AC08M             | AC08M               |

|    |                      | Tape and reel | CD74AC08M96           | ACUOIVI             |

|    | CDIP – F             | Tube          | CD54AC08F3A           | CD54AC08F3A         |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## FUNCTION TABLE (each gate)

| INP | JTS | OUTPUT |

|-----|-----|--------|

| Α   | В   | Y      |

| Н   | Н   | Н      |

| L   | Χ   | L      |

| Х   | L   | L      |

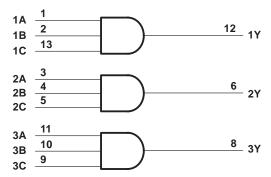

### logic diagram, each gate (positive logic)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCAS532D - AUGUST 1995 - REVISED OCTOBER 2003

- 2-V to 6-V V<sub>CC</sub> Operation

- Inputs Accept Voltages to 6 V

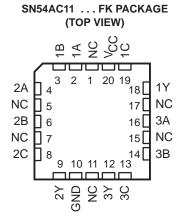

SN54AC11 . . . J OR W PACKAGE SN74AC11 . . . D, DB, N, NS, OR PW PACKAGE (TOP VIEW)

## Max t<sub>pd</sub> of 7.5 ns at 5 V

NC - No internal connection

## description/ordering information

The 'AC11 devices contain three independent 3-input AND gates. These devices perform the Boolean function  $Y = A \cdot B \cdot C$  or  $Y = \overline{A} + \overline{B} + \overline{C}$  in positive logic.

#### **ORDERING INFORMATION**

| TA             | PACKAGE†   |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|----------------|------------|---------------|--------------------------|---------------------|

|                | PDIP – N   | Tube          | SN74AC11N                | SN74AC11N           |

|                | 0010 D     | Tube          | SN74AC11D                | 1044                |

|                | SOIC - D   | Tape and reel | SN74AC11DR               | AC11                |

| -40°C to 85°C  | SOP - NS   | Tape and reel | SN74AC11NSR              | AC11                |

|                | SSOP – DB  | Tape and reel | SN74AC11DBR              | AC11                |

|                | TOCOD DW   | Tube          | SN74AC11PW               | AC44                |

|                | TSSOP – PW | Tape and reel | SN74AC11PWR              | AC11                |

|                | CDIP – J   | Tube          | SNJ54AC11J               | SNJ54AC11J          |

| –55°C to 125°C | CFP – W    | Tube          | SNJ54AC11W               | SNJ54AC11W          |

|                | LCCC - FK  | Tube          | SNJ54AC11FK              | SNJ54AC11FK         |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## FUNCTION TABLE (each gate)

|   | INPUTS |   | OUTPUT |

|---|--------|---|--------|

| Α | В      | С | Y      |

| Н | Н      | Н | Н      |

| L | X      | Χ | L      |

| Х | L      | Χ | L      |

| Х | X      | L | L      |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

1

## SN54AC11, SN74AC11 TRIPLE 3-INPUT POSITIVE-AND GATES

SCAS532D - AUGUST 1995 - REVISED OCTOBER 2003

#### logic diagram, each gate (positive logic)

Pin numbers shown are for the D, DB, J, N, NS, PW, and W packages.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                          |             | –0.5 V to 7 V  |

|----------------------------------------------------------------|-------------|----------------|

| Input voltage range, V <sub>I</sub> (see Note 1)               |             |                |

| Output voltage range, V <sub>O</sub> (see Note 1)              |             |                |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ ). |             | ±20 mA         |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CO}$   | c)          | ±20 mA         |

| Continuous output current, $I_O(V_O = 0 \text{ to } V_{CC})$   |             | ±50 mA         |

| Continuous current through V <sub>CC</sub> or GND              |             | ±200 mA        |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2)        | : D package | 86°C/W         |

|                                                                | DB package  | 96°C/W         |

|                                                                | N package   | 80°C/W         |

|                                                                | NS package  | 76°C/W         |

|                                                                | PW package  | 113°C/W        |

| Storage temperature range, T <sub>stg</sub>                    |             | –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>2.</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

## CD54AC32, CD74AC32 QUADRUPLE 2-INPUT POSITIVE-OR GATES

SCHS343 - MARCH 2003

- AC Types Feature 1.5-V to 5.5-V Operation and Balanced Noise Immunity at 30% of the Supply

- Buffered Inputs

- Speed of Bipolar F, AS, and S, With Significantly Reduced Power Consumption

- Balanced Propagation Delays

- ±24-mA Output Drive Current

- Fanout to 15 F Devices

- SCR-Latchup-Resistant CMOS Process and Circuit Design

- Exceeds 2-kV ESD Protection Per MIL-STD-883, Method 3015

#### CD54AC32...F PACKAGE CD74AC32...E OR M PACKAGE (TOP VIEW) 14 🛮 V<sub>CC</sub> 1A [ 13 4B 1B **∏** 2 1Y 🛮 3 12 4A 2A 🛮 4 11 🛮 4Y 10 3B 2B 🛮 5 9 🛮 3A 2Y 6 8 3Y GND [] 7

#### description/ordering information

The 'AC32 devices are quadruple 2-input positive-OR gates. These devices perform the Boolean function  $Y = \overline{\overline{A} \bullet \overline{B}}$  or Y = A + B in positive logic.

#### ORDERING INFORMATION

| TA             | PACKAGE <sup>†</sup> |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|----------------|----------------------|---------------|--------------------------|---------------------|

|                | PDIP – E             | Tube          | CD74AC32E                | CD74AC32E           |

| –55°C to 125°C | SOIC - M             | Tube          | CD74AC32M                | AC32M               |

|                |                      | Tape and reel | CD74AC32M96              | AC32IVI             |

|                | CDIP – F             | Tube          | CD54AC32F3A              | CD54AC32F3A         |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## FUNCTION TABLE (each gate)

| · • · |     |        |  |  |  |

|-------|-----|--------|--|--|--|

| INP   | UTS | OUTPUT |  |  |  |

| Α     | В   | Υ      |  |  |  |

| Н     | Х   | Н      |  |  |  |

| Х     | Н   | Н      |  |  |  |

| L     | L   | L      |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCHS343 - MARCH 2003

### logic diagram (positive logic)

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                                                                        | 0.5 V to 6 V   |

|--------------------------------------------------------------------------------------------------------------|----------------|

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>CC</sub> ) (see Note 1)  | ±20 mA         |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see Note 1) | ±50 mA         |

| Continuous output current, $I_O$ ( $V_O = 0$ to $V_{CC}$ )                                                   | ±50 mA         |

| Continuous current through V <sub>CC</sub> or GND                                                            | ±100 mA        |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2): E package                                           | 80°C/W         |

| M package                                                                                                    | 86°C/W         |

| Storage temperature range, T <sub>stq</sub>                                                                  | –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions (see Note 3)

|                |                                    |                                            | T <sub>A</sub> = 2 | 25°C | –55°0<br>125 |      | –40°(<br>85° |      | UNIT   |

|----------------|------------------------------------|--------------------------------------------|--------------------|------|--------------|------|--------------|------|--------|

|                |                                    |                                            | MIN                | MAX  | MIN          | MAX  | MIN          | MAX  |        |

| VCC            | Supply voltage                     |                                            | 1.5                | 5.5  | 1.5          | 5.5  | 1.5          | 5.5  | V      |

|                |                                    | V <sub>CC</sub> = 1.5 V                    | 1.2                |      | 1.2          |      | 1.2          |      |        |

| VIН            | High-level input voltage           | V <sub>CC</sub> = 3 V                      | 2.1                |      | 2.1          |      | 2.1          |      | V      |

|                |                                    | V <sub>CC</sub> = 5.5 V                    | 3.85               |      | 3.85         |      | 3.85         |      |        |

|                |                                    | V <sub>CC</sub> = 1.5 V                    |                    | 0.3  |              | 0.3  |              | 0.3  |        |

| $V_{IL}$       | Low-level input voltage            | V <sub>CC</sub> = 3 V                      |                    | 0.9  |              | 0.9  |              | 0.9  | V      |

|                |                                    | V <sub>CC</sub> = 5.5 V                    |                    | 1.65 |              | 1.65 |              | 1.65 |        |

| ٧ <sub>I</sub> | Input voltage                      |                                            | 0                  | VCC  | 0            | VCC  | 0            | VCC  | V      |

| ٧o             | Output voltage                     |                                            | 0                  | VCC  | 0            | VCC  | 0            | VCC  | V      |

| ЮН             | High-level output current          | V <sub>CC</sub> = 4.5 V to 5.5 V           |                    | -24  |              | -24  |              | -24  | mA     |

| loL            | Low-level output current           | V <sub>CC</sub> = 4.5 V to 5.5 V           |                    | 24   |              | 24   |              | 24   | mA     |

| Δt/Δν          | Input transition rise or fall rate | V <sub>CC</sub> = 1.5 V to 3 V             |                    | 50   |              | 50   |              | 50   | ns/V   |

| ΔυΔν           | Input transition rise or fall rate | $V_{CC} = 3.6 \text{ V to } 5.5 \text{ V}$ |                    | 20   |              | 20   |              | 20   | 115/ V |

NOTE 3: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>2.</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

SCAS534C - AUGUST 1995 - REVISED OCTOBER 2003

- 4.5-V to 5.5-V V<sub>CC</sub> Operation

- Inputs Accept Voltages to 5.5 V

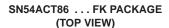

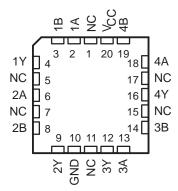

SN54ACT86... J OR W PACKAGE SN74ACT86... D, DB, N, NS, OR PW PACKAGE (TOP VIEW)

- Max t<sub>pd</sub> of 10 ns at 5 V

- Inputs Are TTL-Voltage Compatible

NC - No internal connection

## description/ordering information

The 'ACT86 devices are quadruple 2-input exclusive-OR gates. The devices perform the Boolean functions  $Y = A \oplus B$  or  $Y = \overline{AB} + A\overline{B}$  in positive logic.

A common application is as a true/complement element. If one of the inputs is low, the other input is reproduced in true form at the output. If one of the inputs is high, the signal on the other input is reproduced inverted at the output.

#### **ORDERING INFORMATION**

| TA             | PACKAGE <sup>†</sup> |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|----------------|----------------------|---------------|--------------------------|---------------------|

|                | PDIP – N             | Tube          | SN74ACT86N               | SN74ACT86N          |

|                | 0010 D               | Tube          | SN74ACT86D               | AOT00               |

|                | SOIC - D             | Tape and reel | SN74ACT86DR              | ACT86               |

| -40°C to 85°C  | SOP - NS             | Tape and reel | SN74ACT86NSR             | ACT86               |

|                | SSOP – DB            | Tape and reel | SN74ACT86DBR             | AD86                |

|                | TOCOD DW             | Tube          | SN74ACT86PW              | ADOC                |

|                | TSSOP – PW           | Tape and reel | SN74ACT86PWR             | AD86                |

|                | CDIP – J             | Tube          | SNJ54ACT86J              | SNJ54ACT86J         |

| –55°C to 125°C | CFP – W              | Tube          | SNJ54ACT86W              | SNJ54ACT86W         |

|                | LCCC – FK            | Tube          | SNJ54ACT86FK             | SNJ54ACT86FK        |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **FUNCTION TABLE** (each gate)

| INPUTS |   | OUTPUT |

|--------|---|--------|

| Α      | В | Υ      |

| L      | L | L      |

| L      | Н | Н      |

| Н      | L | Н      |

| Н      | Н | L      |

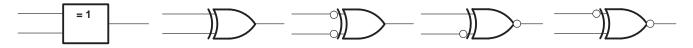

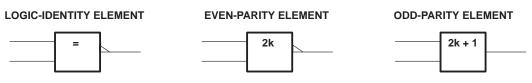

#### exclusive-OR logic

An exclusive-OR gate has many applications, some of which can be represented better by alternative logic symbols.

#### **EXCLUSIVE-OR**

These five equivalent exclusive-OR symbols are valid for an 'ACT86 gate in positive logic; negation may be shown at any two ports.

The output is active (low) if all inputs stand at the same logic level (i.e., A = B).

The output is active (low) if an even number of inputs (i.e., 0 or 2) are active.

The output is active (high) if an odd number of inputs (i.e., only 1 of the 2) are active.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub>                                                        |              | 0.5 V to 7 V                               |

|----------------------------------------------------------------------------------------------|--------------|--------------------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                                             |              |                                            |

| Output voltage range, VO (see Note 1)                                                        |              | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ ).                               |              | ±20 mA                                     |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>C</sub> | C)           | ±20 mA                                     |

| Continuous output current, $I_O(V_O = 0 \text{ to } V_{CC})$                                 |              | ±50 mA                                     |

| Continuous current through V <sub>CC</sub> or GND                                            |              | ±200 mA                                    |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2)                                      | ): D package | 86°C/W                                     |

| , , , , , , , , , , , , , , , , , , , ,                                                      | DB package   | 96°C/W                                     |

|                                                                                              | N package    | 80°C/W                                     |

|                                                                                              | NS package   | 76°C/W                                     |

|                                                                                              | PW package   | 113°C/W                                    |

| Storage temperature range, T <sub>stg</sub>                                                  |              | –65°C to 150°C                             |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51-7.